# **Maintenance Manual**

**Compucolor** Corporation

P.O. Box 569 Norcross, Georgia 30071 Telephone 404/449-5996

# Compucolor<sup>®</sup> II Maintenance Manual

## PROPRIETARY STATEMENT

This document, submitted in confidence, contains proprietary information which shall not be reproduced or transferred to other documents or disclosed to others or used for manufacturing or any other purpose without prior written permission of Compucolor Corporation.

## TABLE OF CONTENTS

| SECTION |                                                                                                                                             | PAGE                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| I       | Specifications                                                                                                                              | 1.01                                                                 |

| II      | Installation                                                                                                                                | 2.01                                                                 |

|         | Standard<br>RS-232 Modem<br>Add-ons                                                                                                         | 2.01<br>2.01<br>2.02                                                 |

| III     | Operation                                                                                                                                   | 3.01                                                                 |

| IV      | System Description                                                                                                                          |                                                                      |

|         | Software<br>Hardware                                                                                                                        | 4.01<br>4.02                                                         |

| V       | Subassembly Descriptions                                                                                                                    |                                                                      |

|         | CRT, Yoke and Cabinet Power Board Analog Board Logic Board Video Board Disk Drive Keyboard Add-on PROM Add-on RAM                           | 5.01<br>5.01<br>5.03<br>5.16<br>5.26<br>5.26<br>5.28<br>5.29<br>5.30 |

| VI      | Maintenance                                                                                                                                 |                                                                      |

|         | Safety Precautions Servicing Precautions Preventive Maintenance Cabinet Disassembly Alignment Operational Test Trouble-Shooting Information | 6.01<br>6.02<br>6.02<br>6.03<br>6.04<br>6.11                         |

| VII     | Parts List                                                                                                                                  |                                                                      |

## TABLE OF CONTENTS - continued

| VIII | Drawings                      | Drawing No.  |

|------|-------------------------------|--------------|

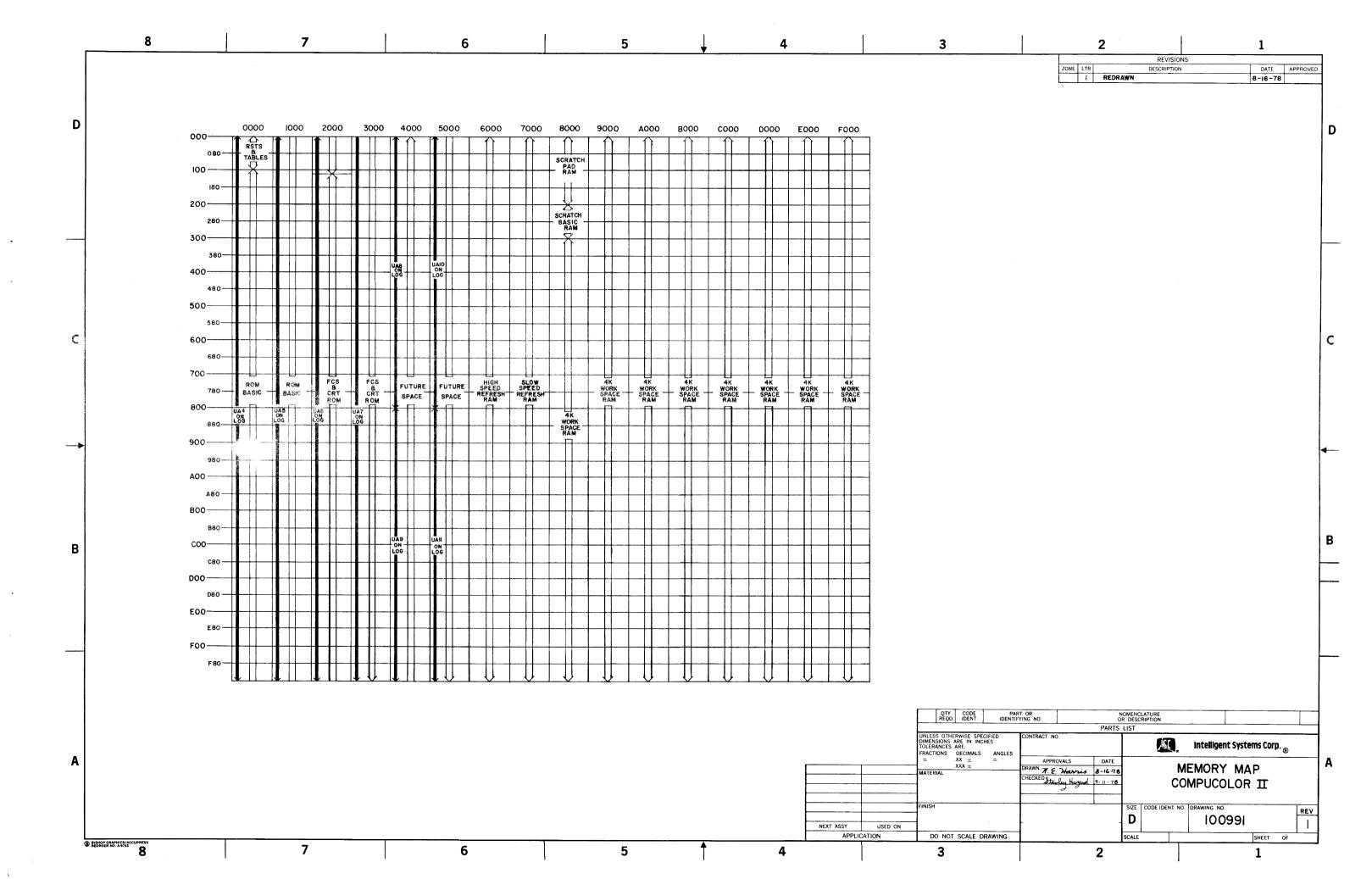

|      | Memory Map                    | 100991       |

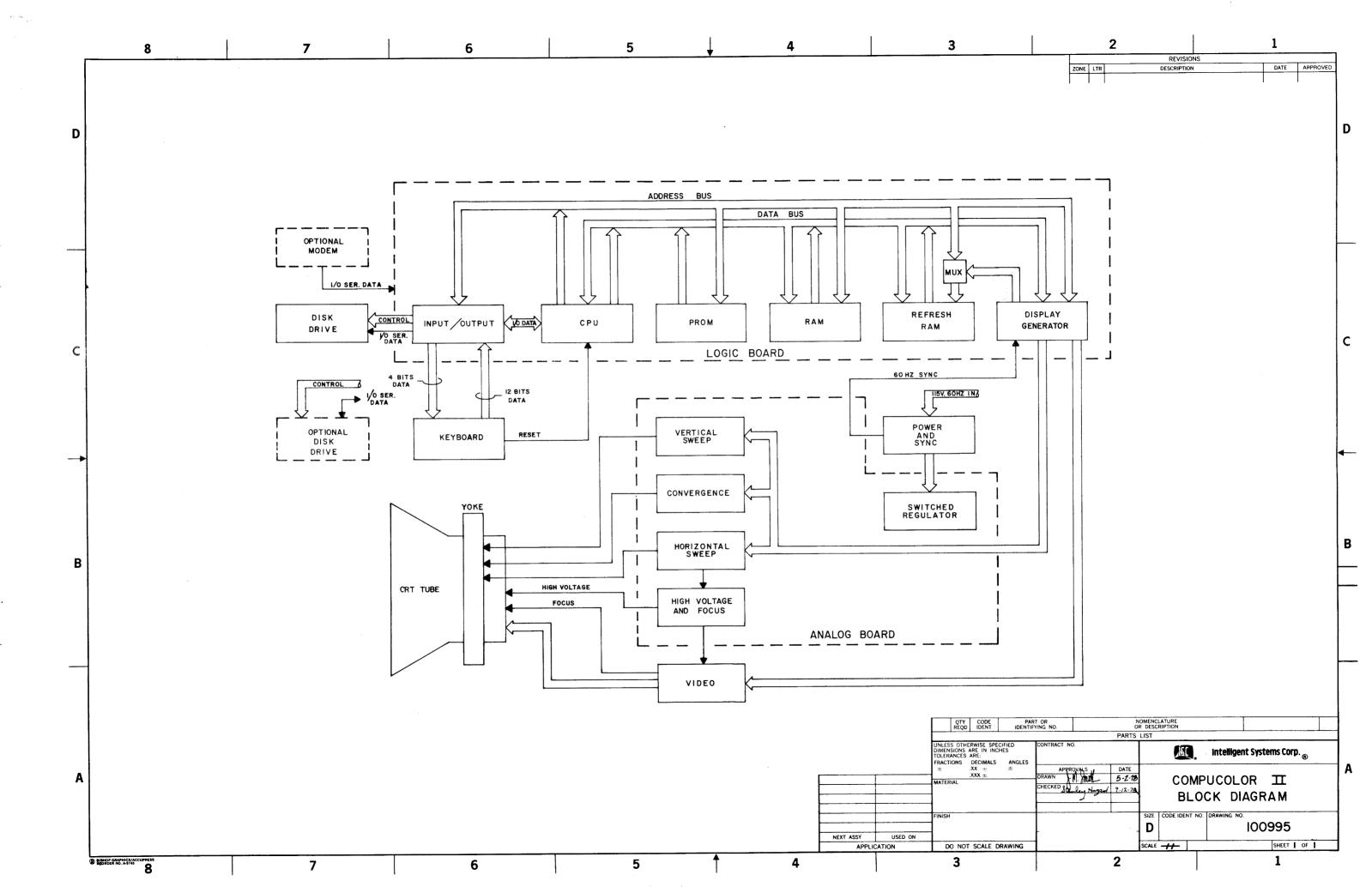

|      | Block Diagram                 | 100995       |

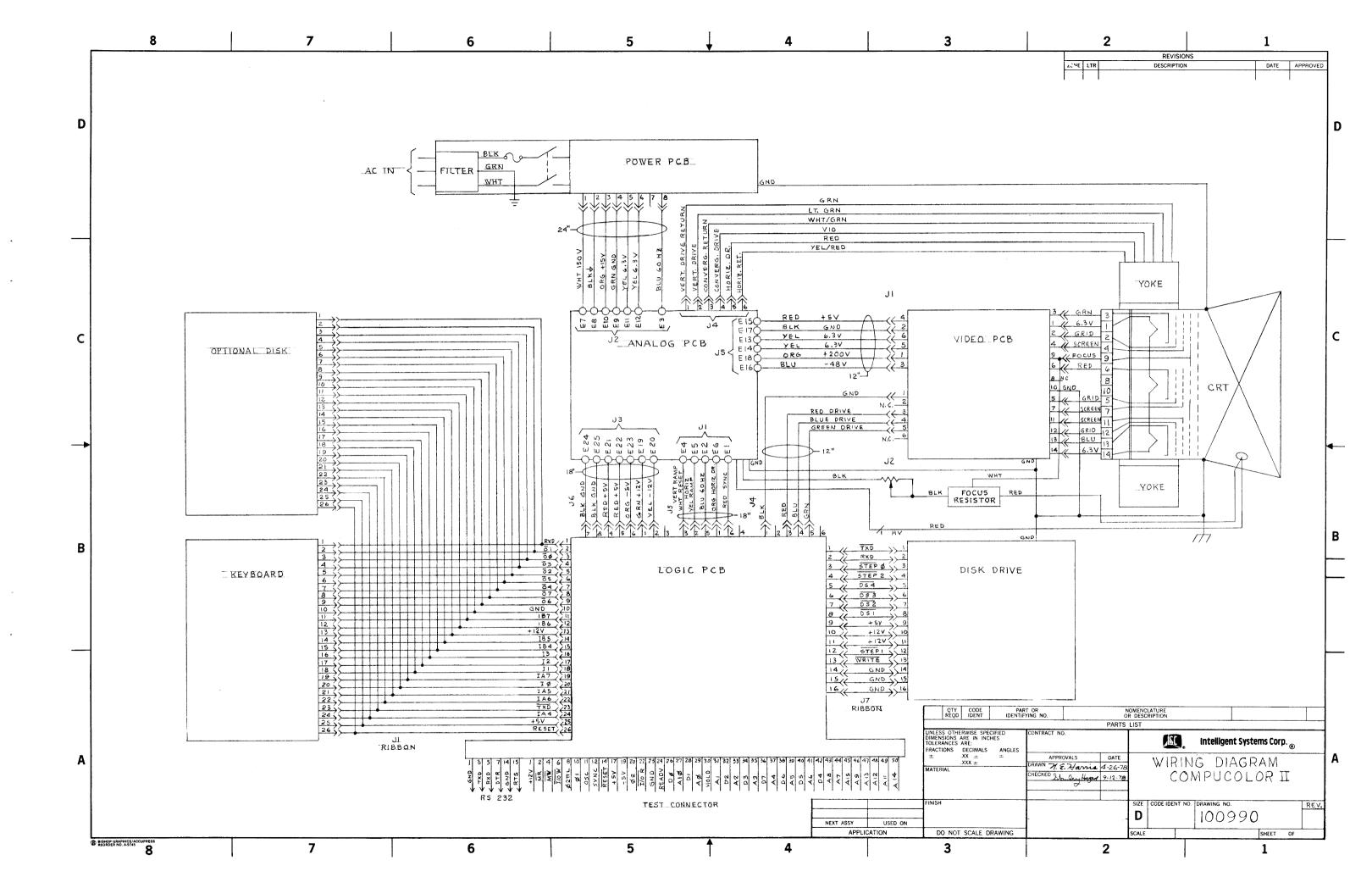

|      | Wiring Diagram                | 100990       |

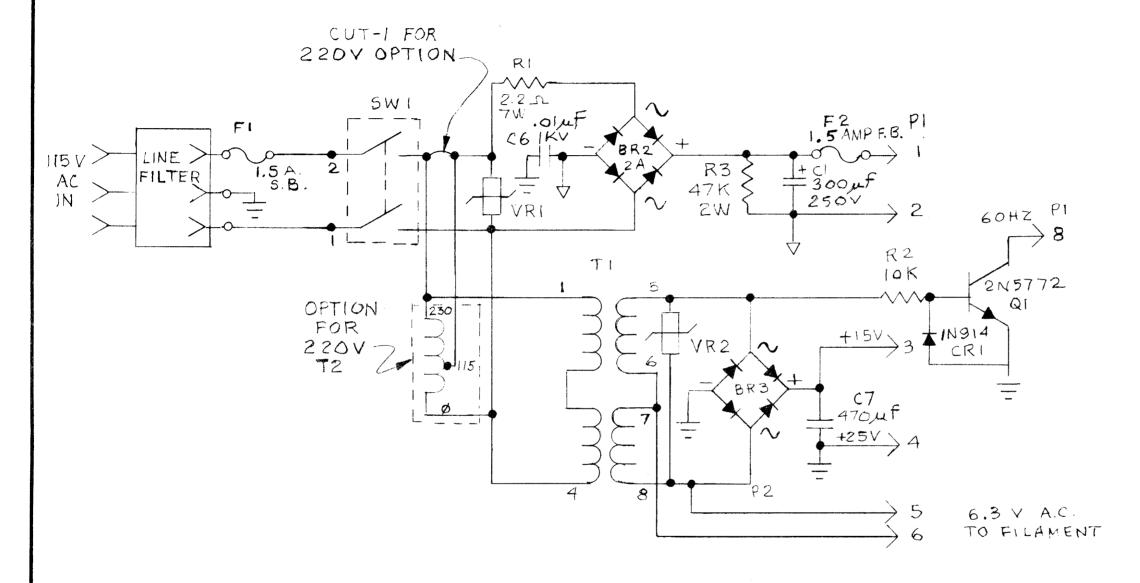

|      | Power Board Schematic         | 100903       |

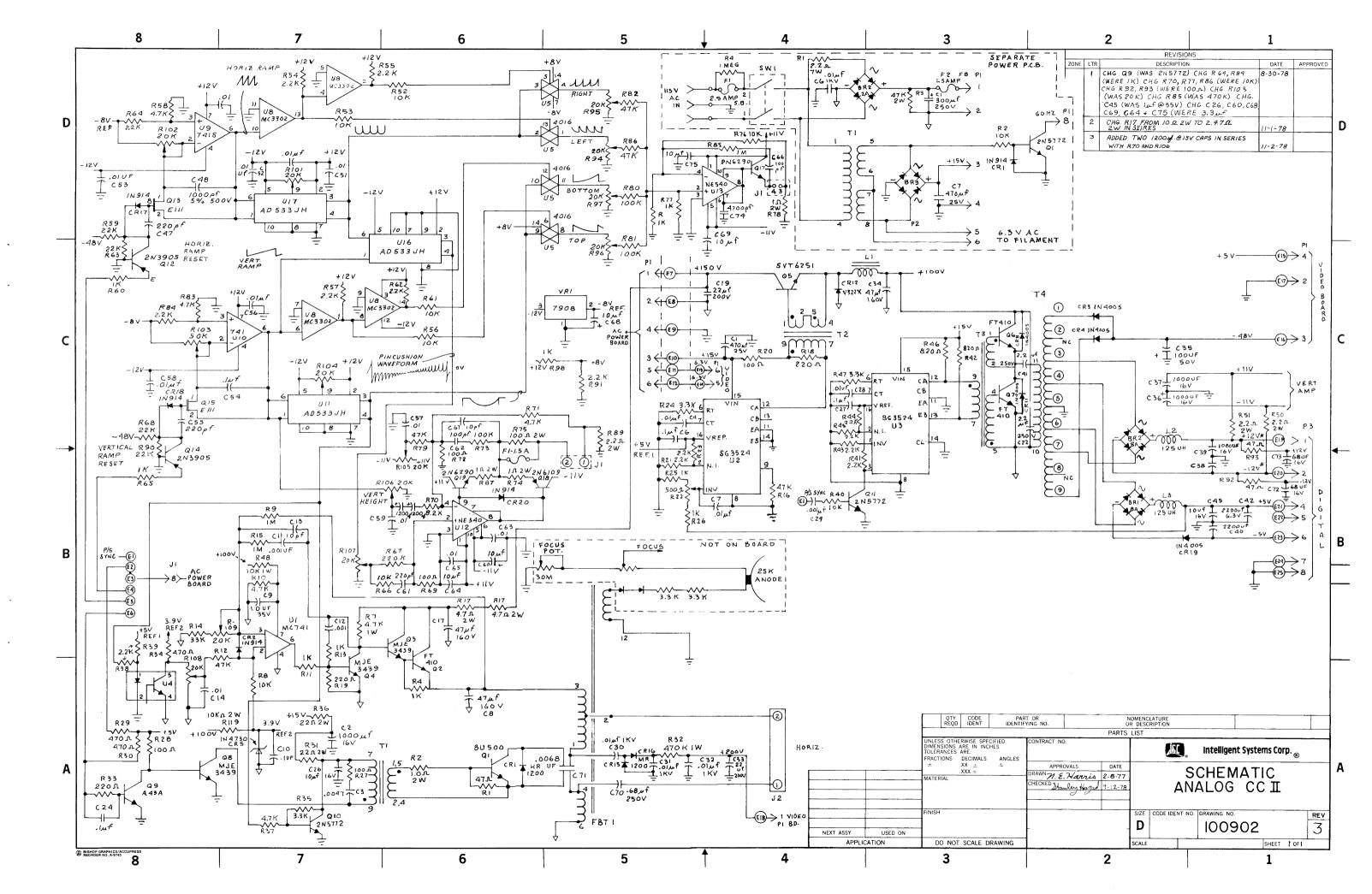

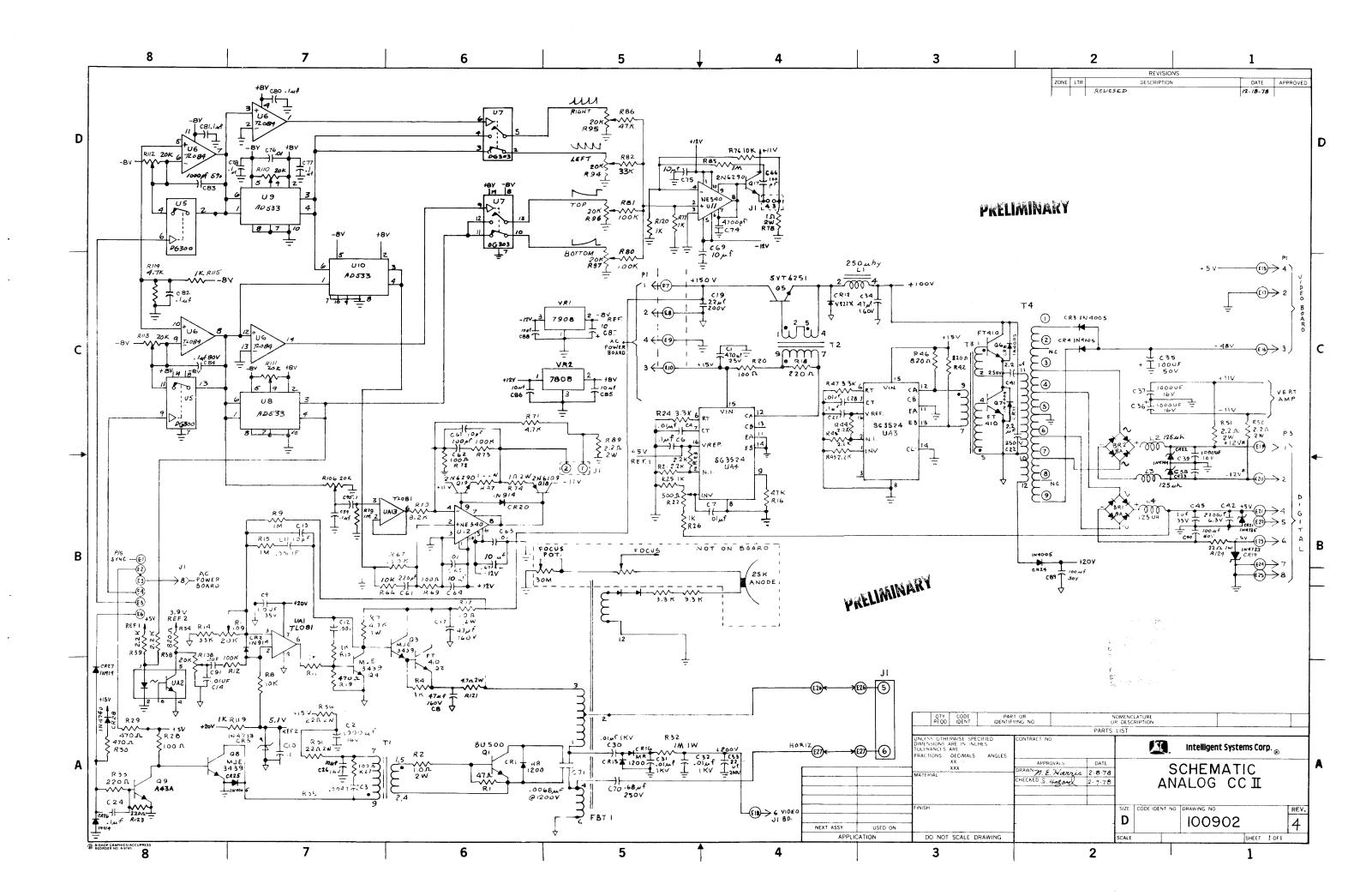

|      | Analog Board Schematic Rev.3  | 100902       |

|      | Analog Board Schematic Rev.4  | 100902       |

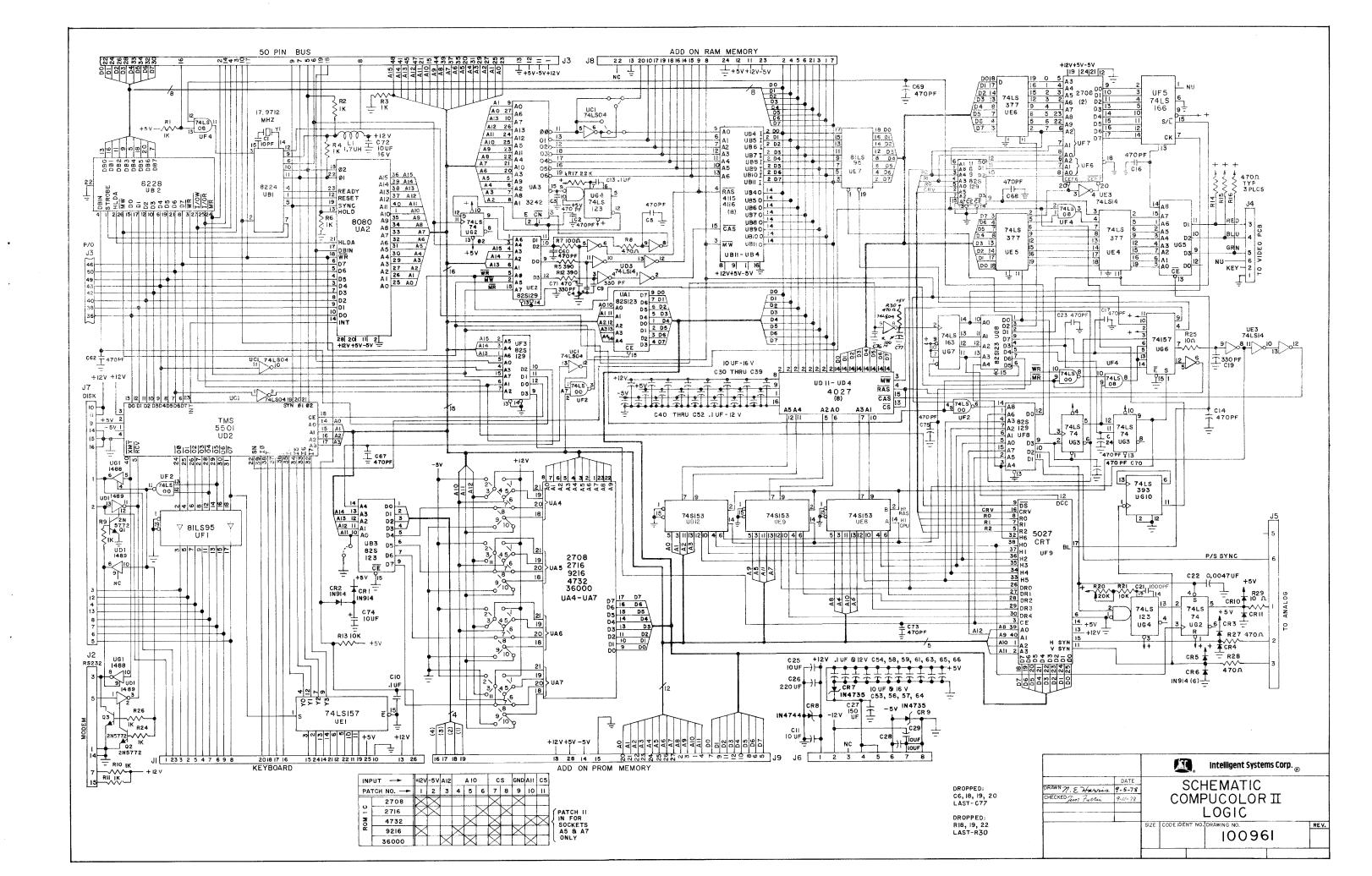

|      | Logic Board Schematic         | 100961       |

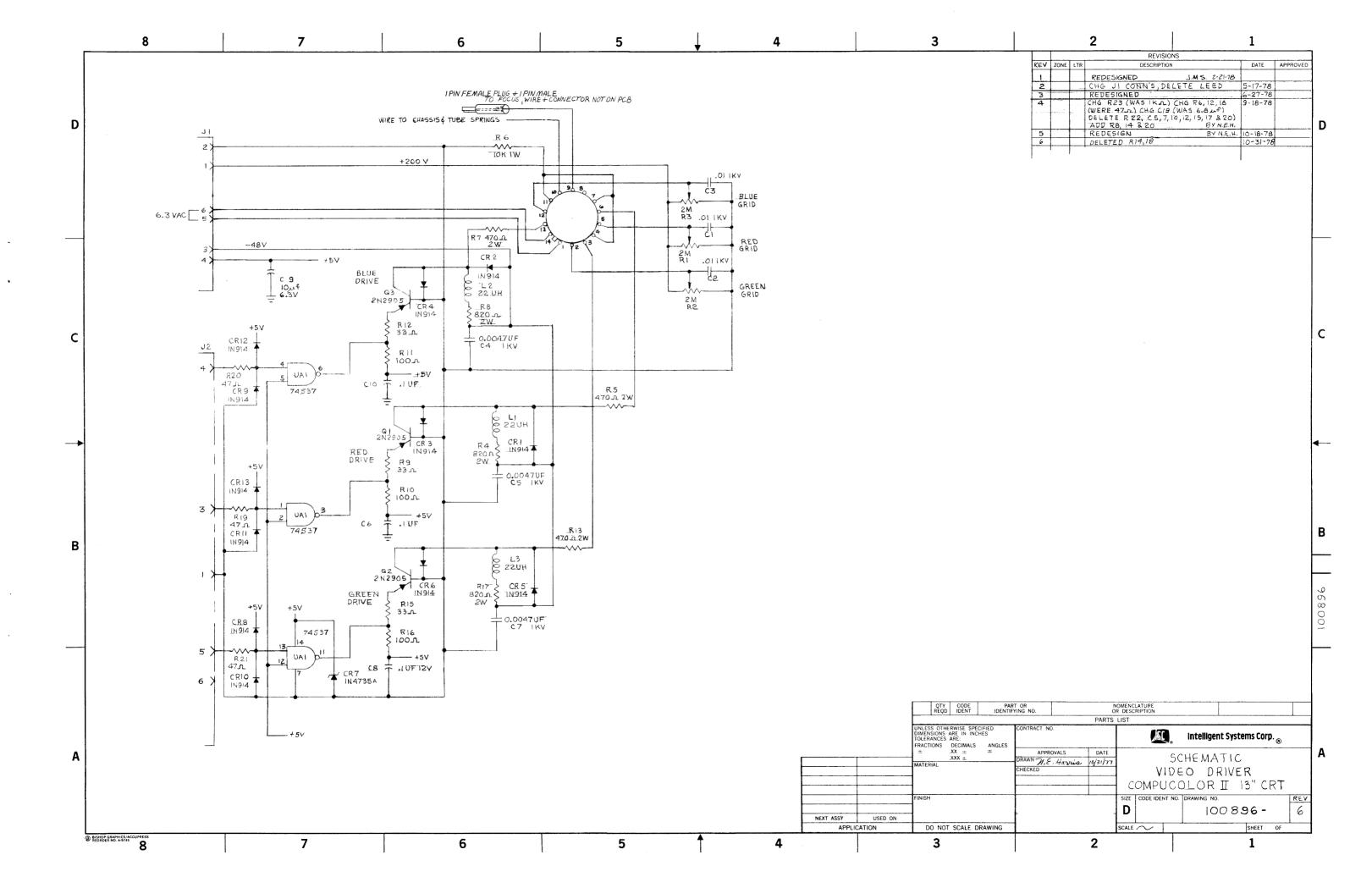

|      | Video Board Schematic         | 100896       |

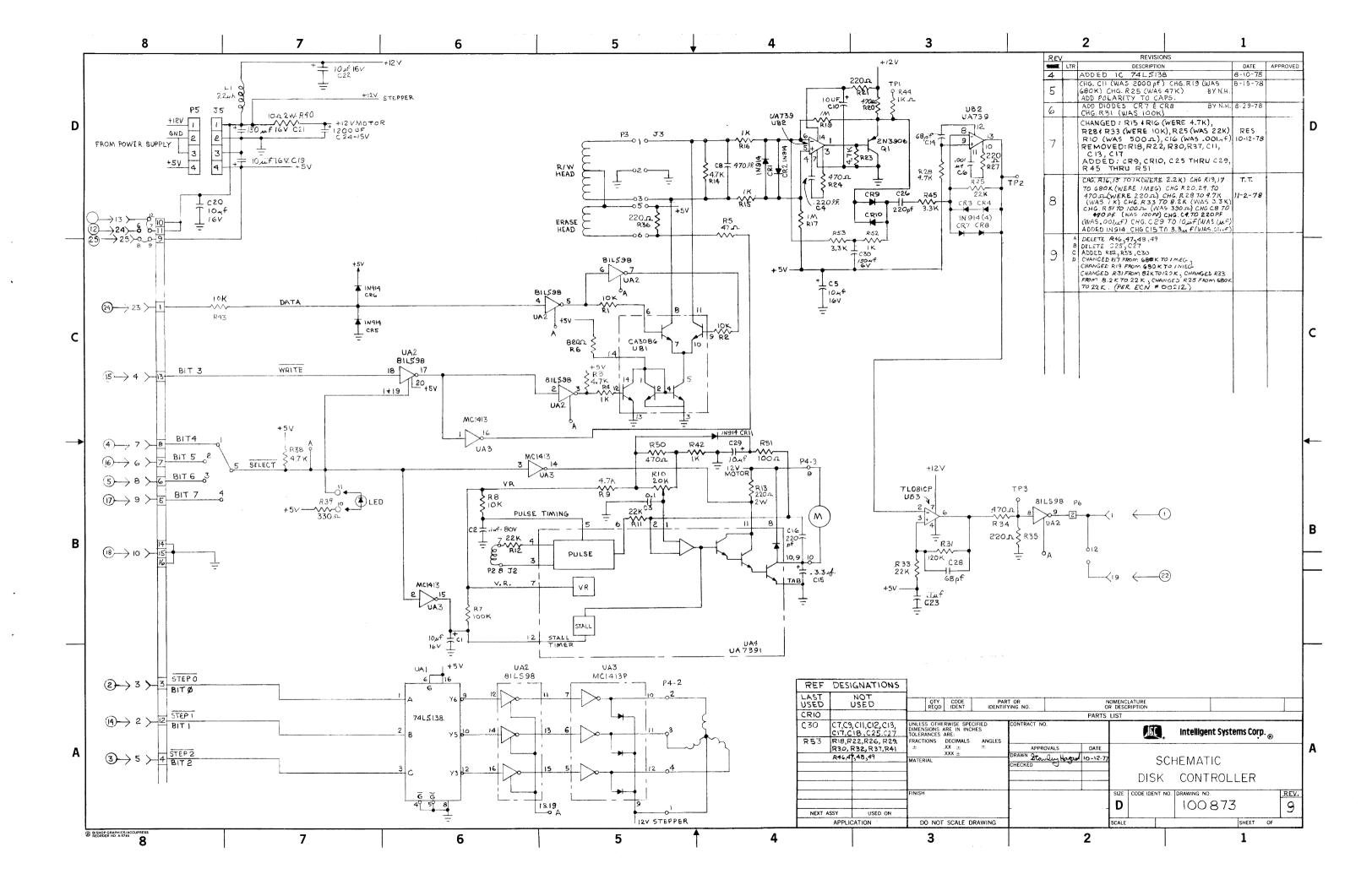

|      | Disk Controller Schematic     | 100873       |

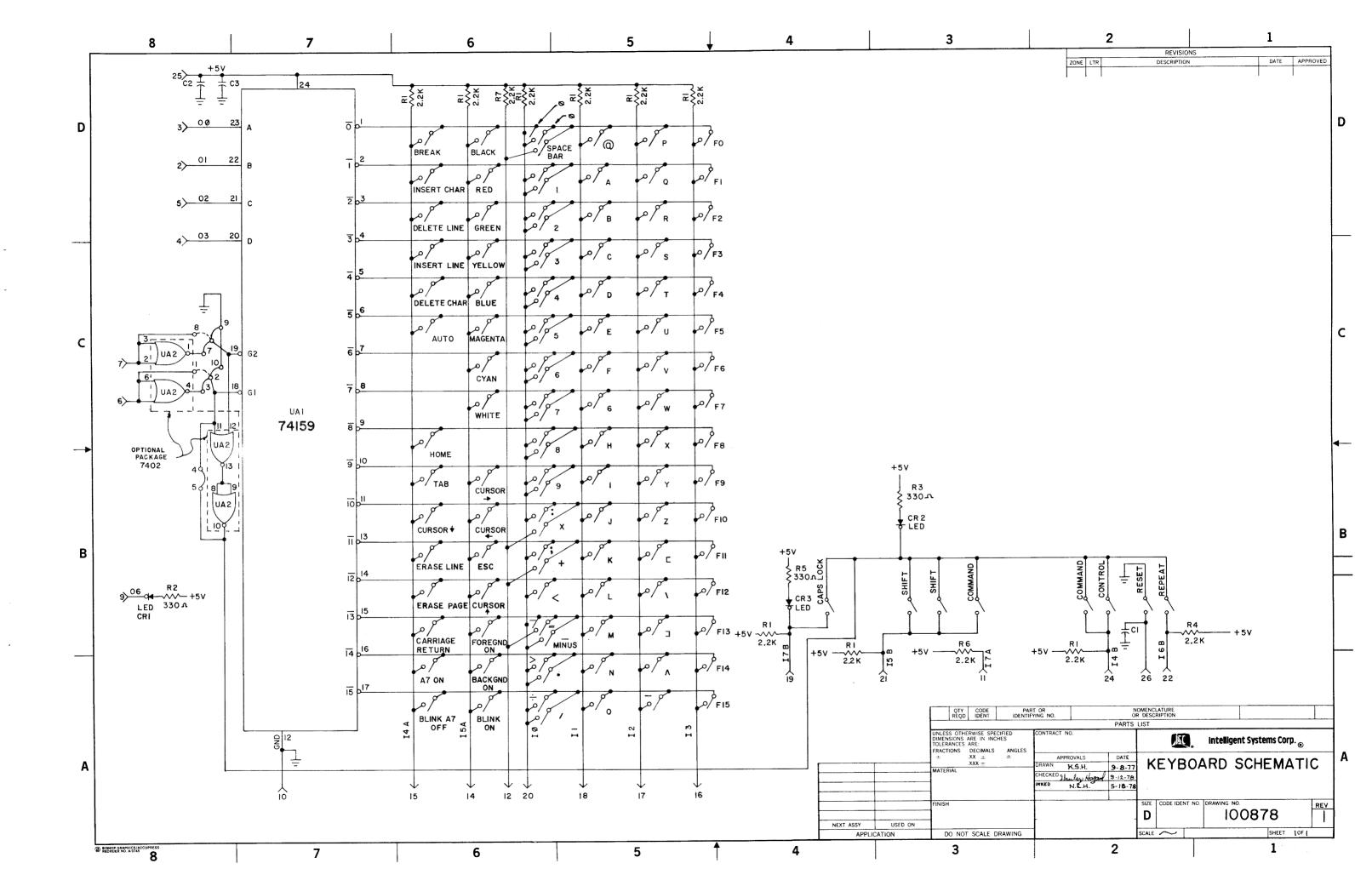

|      | Keyboard Schematic            | 100878       |

|      | Add-on PROM Schematic         | 100979       |

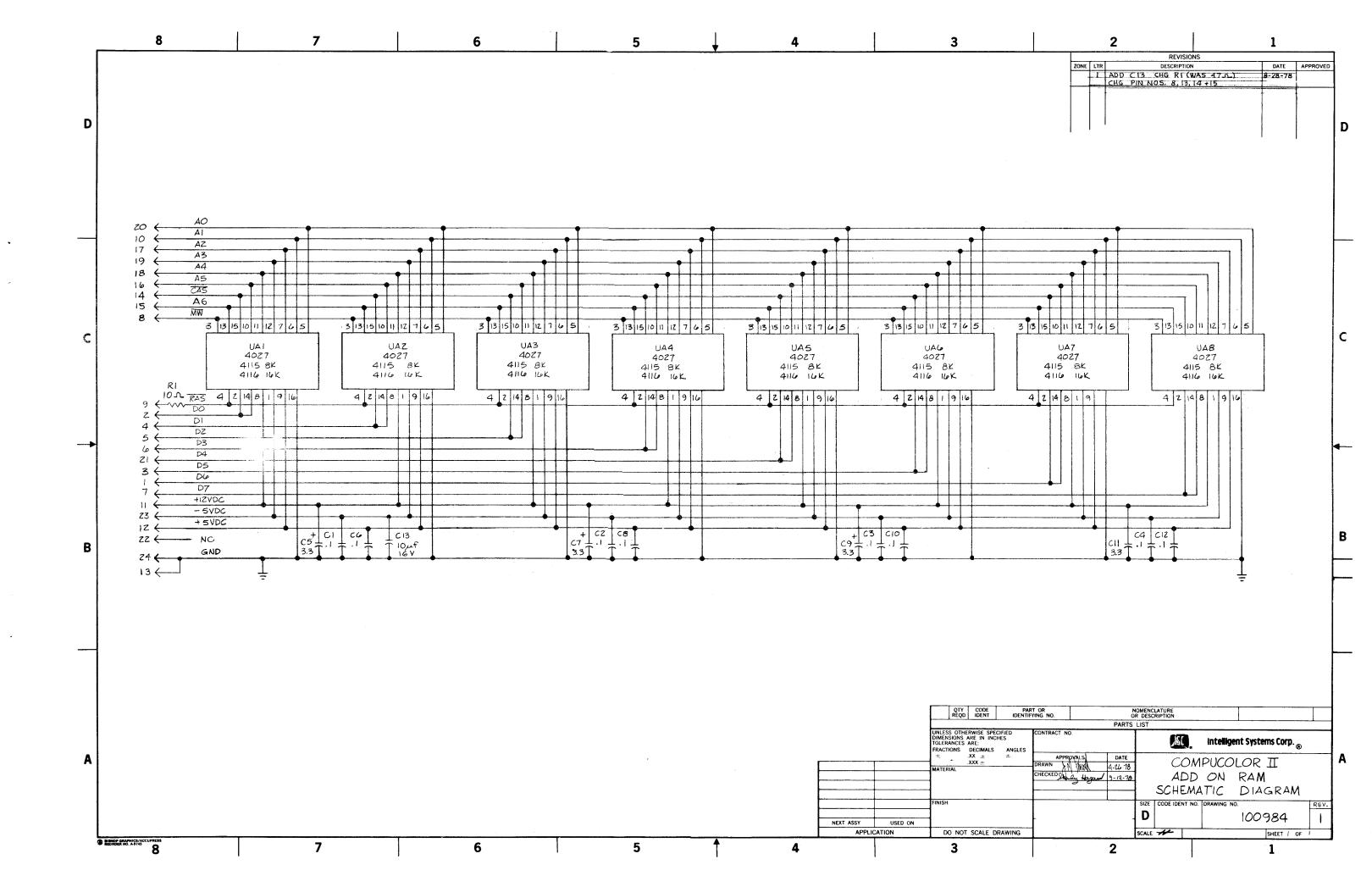

|      | Add-on RAM Schematic          | 100984       |

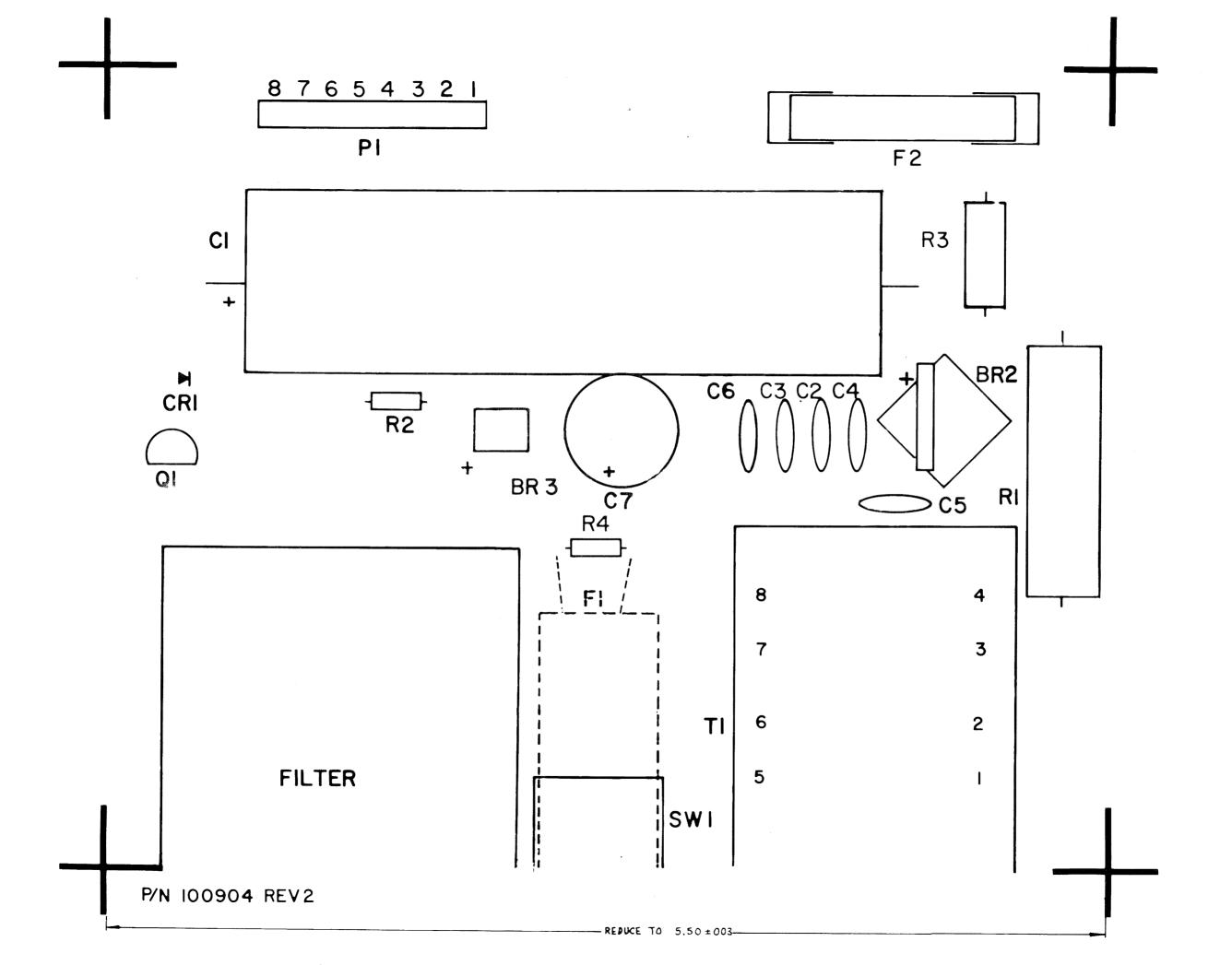

|      | Power PCB                     | 100904       |

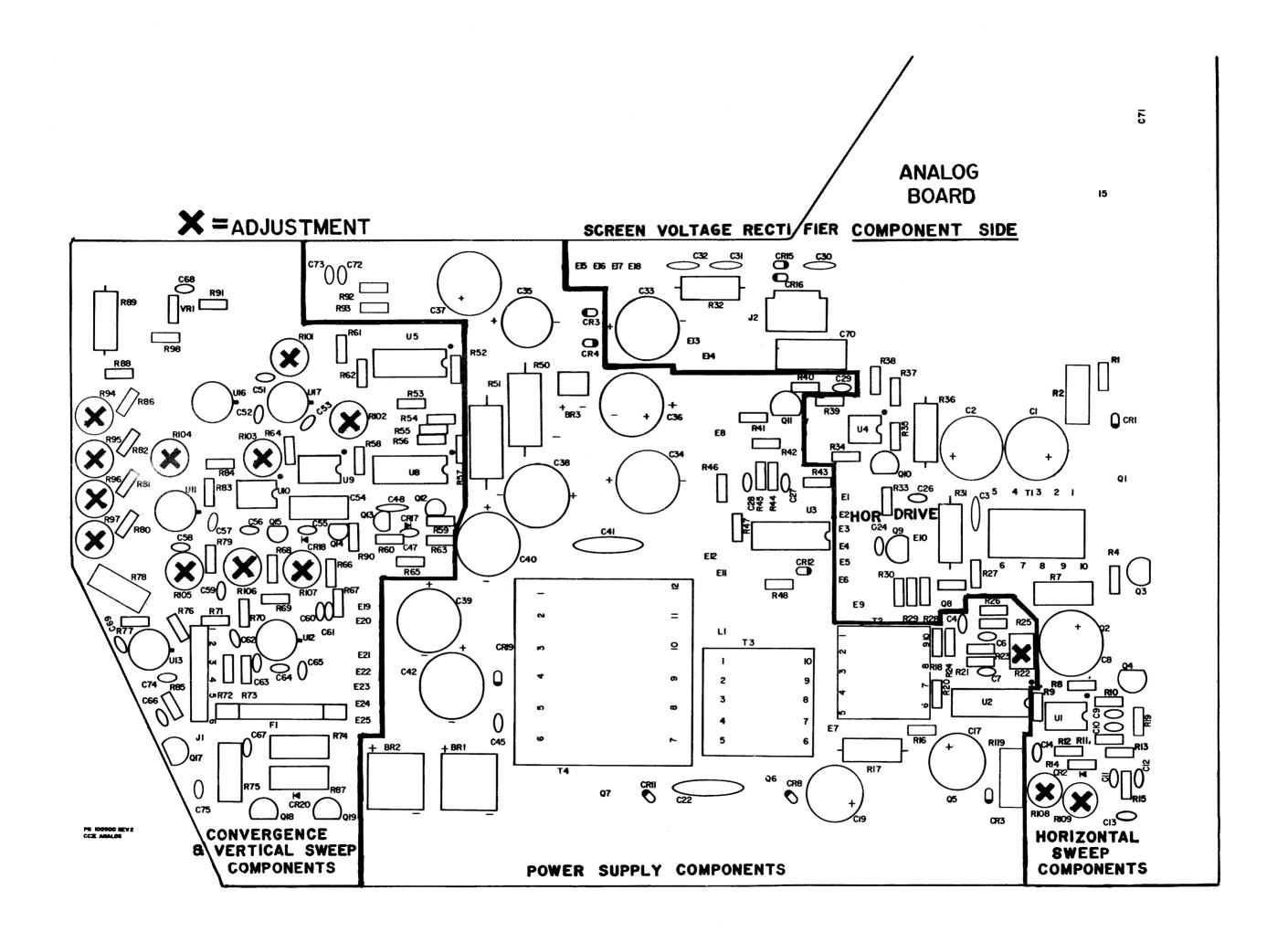

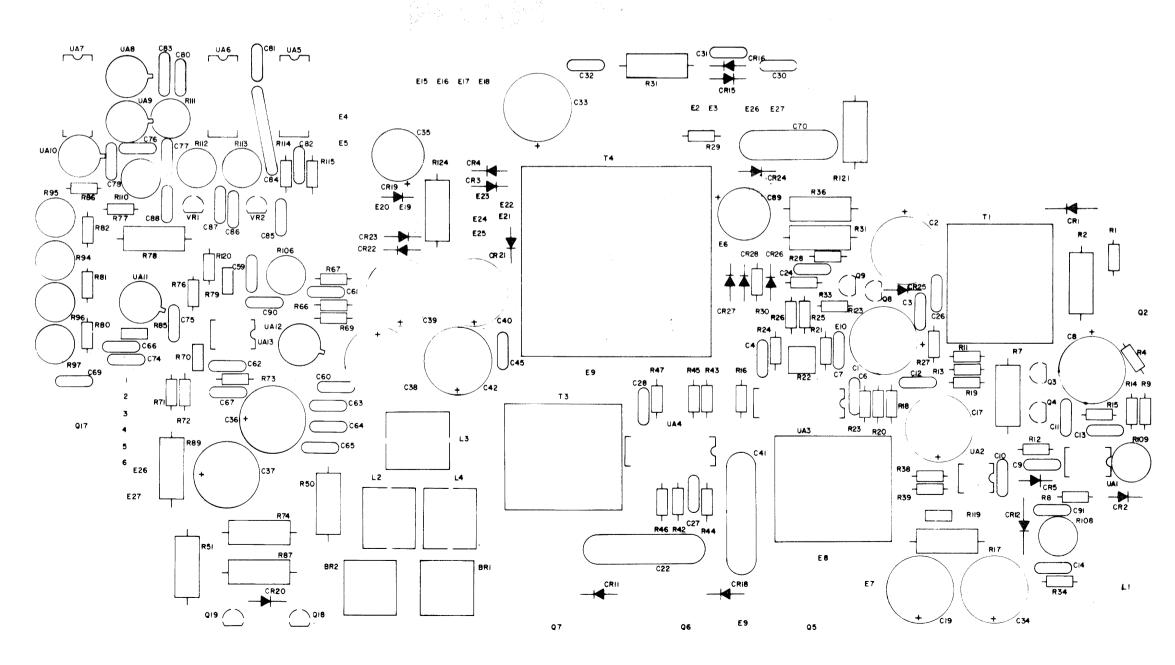

|      | Analog PCB Rev.2              | 100900       |

|      | Analog PCB Rev.3              | 100900       |

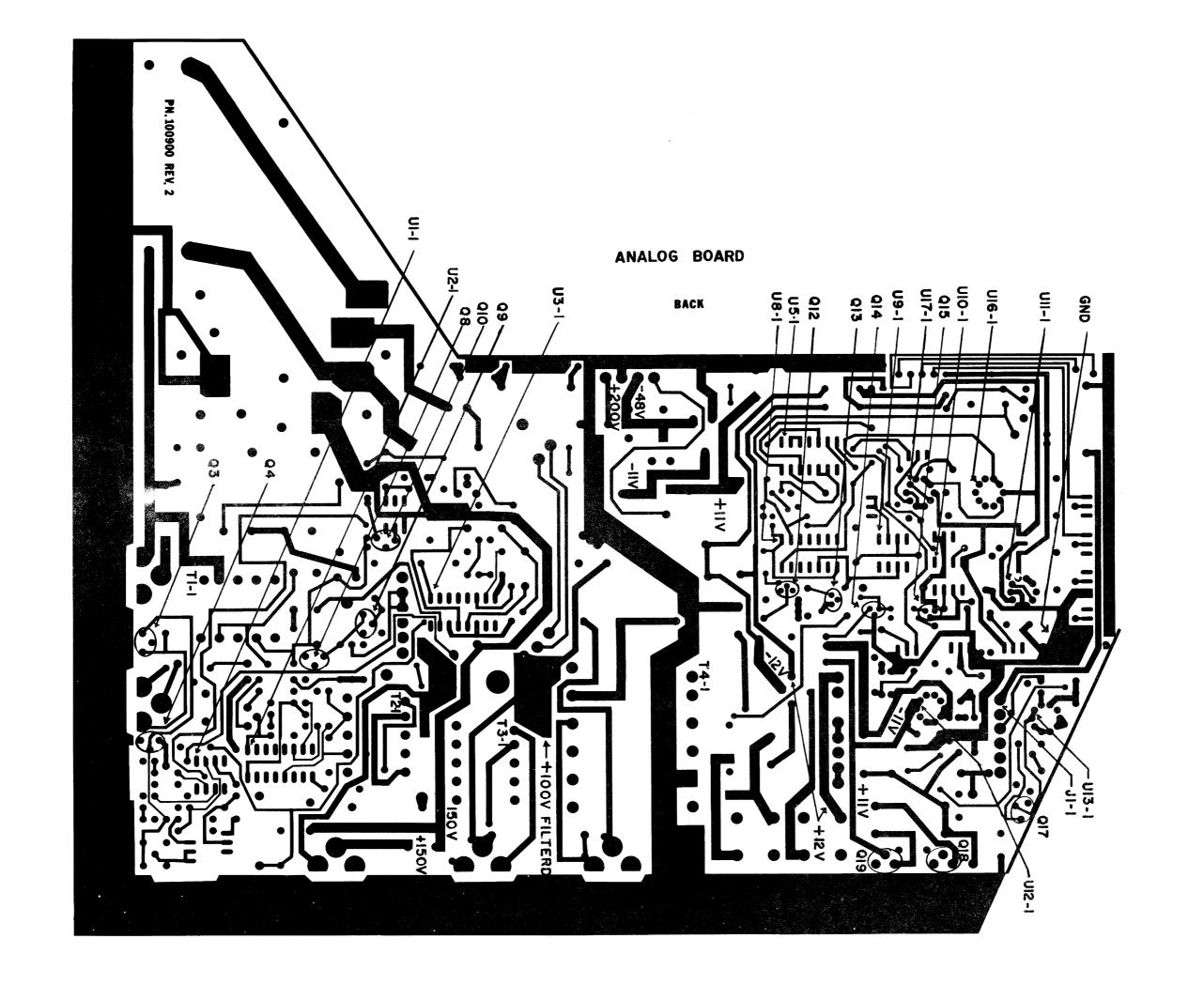

|      | Analog Board Back Side Wiring | 100900       |

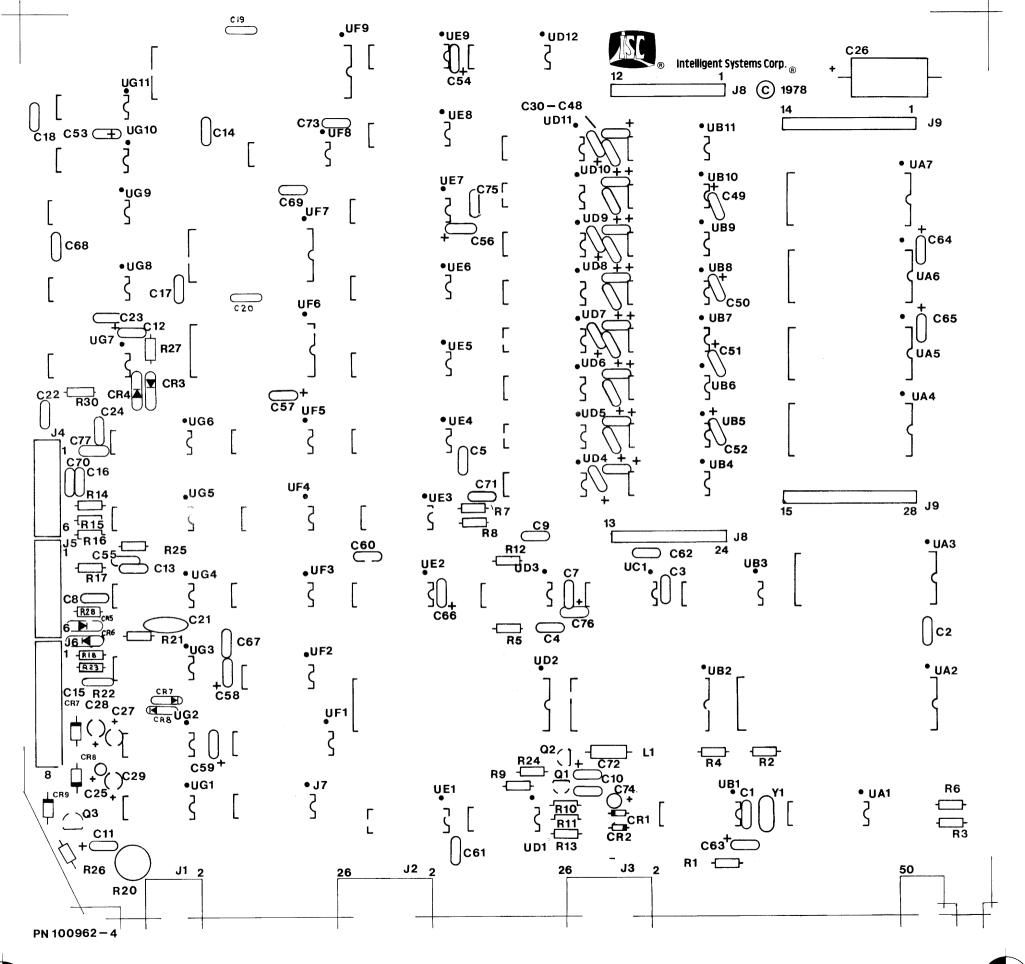

|      | Logic PCB                     | 100962       |

|      | Video PCB                     | 100894       |

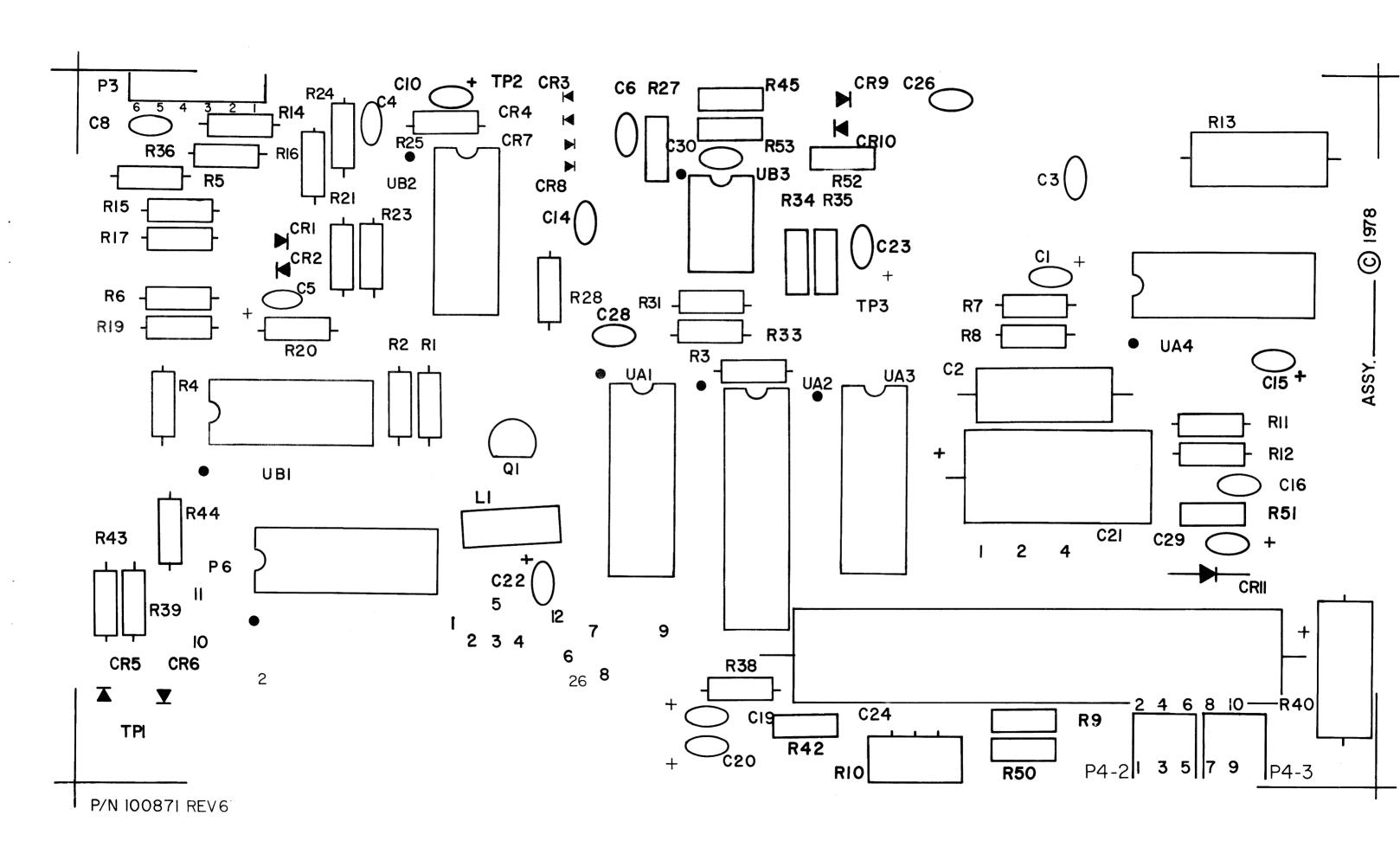

|      | Disk Controller PCB           | 100871       |

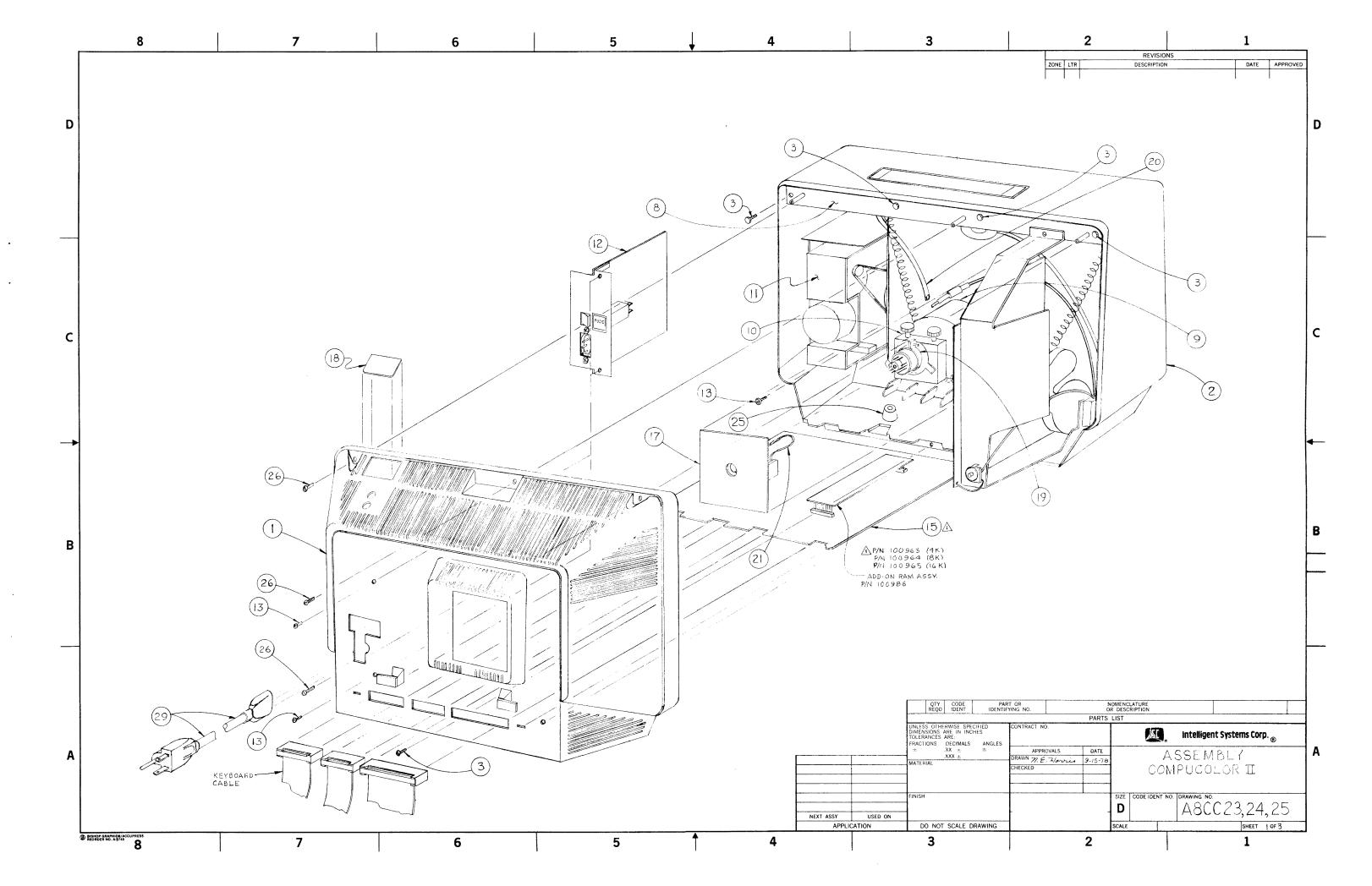

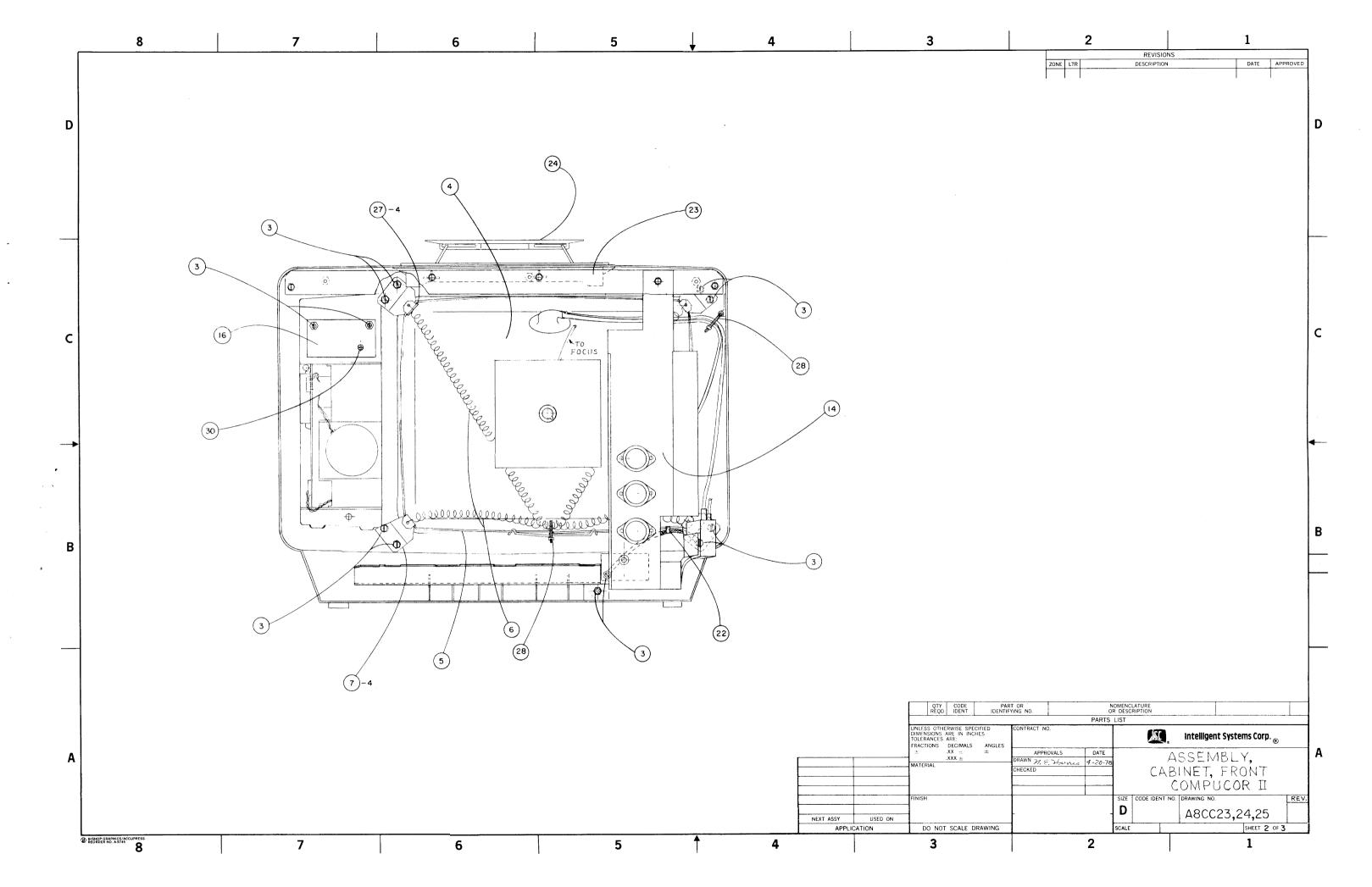

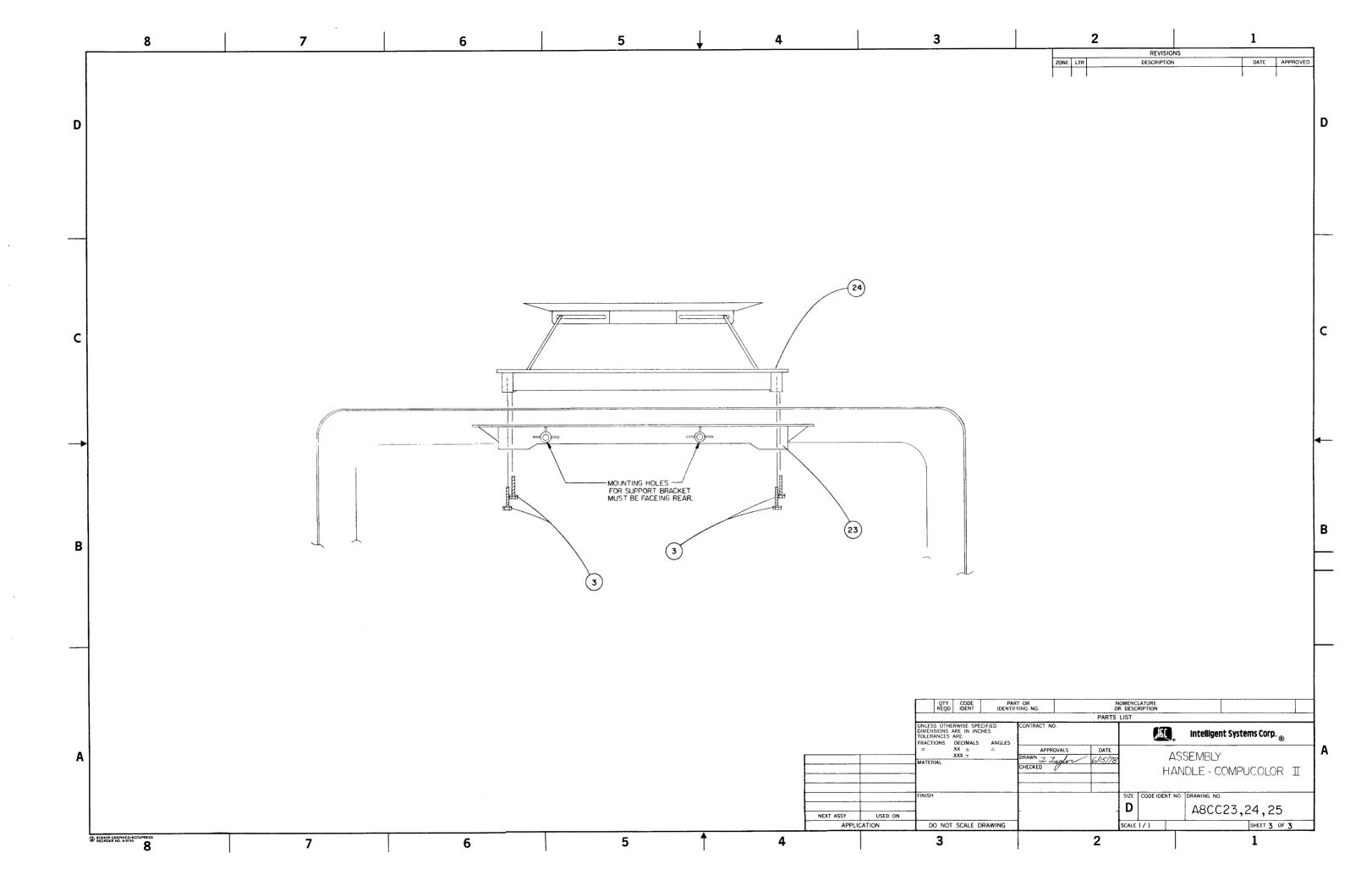

|      | Cabinet Assembly              | A8CC23,24,25 |

NOTE: See Section VII for Assembly Part Numbers.

PCB Numbers shown above refer to bare PCB only.

SECTION I COMPUCOLOR II SPECIFICATIONS

### I. SPECIFICATIONS

## Operating Conditions

Power

Temperature

Humidity

## Physical Dimensions

Cabinet Keyboard Weight Shipping Weight Screen Size

## Performance

CRT Display

Keyboard

105-125 Volts, 50/60 HZ., 150 Watts +  $10^{\circ}$  C to +  $40^{\circ}$  C Operating -  $30^{\circ}$  C to +  $70^{\circ}$  C for storage only 0 to 95% non-condensing

18.0" W x 13.6" H x 15.8" D

18.7" W x 2.8" H x 6.9" D

37 pounds, including keyboard

45 pounds complete

13 inch diagonal, 90 square inches in area

Display normally uses 60 to 70 square inches.

Eight colors, background and foreground

(red,green,blue,magenta,cyan,yellow,white

and black)

64 Characters per line 32 lines per page, or 16 lines with 2X character height

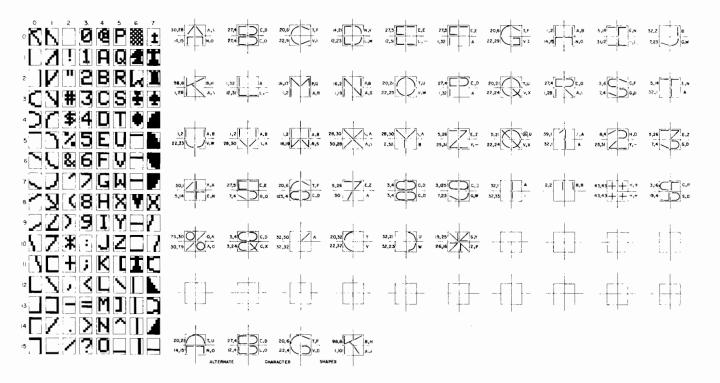

64 ASCII characters, 5 x 7 dot matrix within a 6 x 8 dot pattern, plus 64 special characters in a 6 x 8 matrix. Expandable to include graphics of  $128 \times 128$  and vector generating software. Cursor is white blinking overscore and underscore, non-destructive.

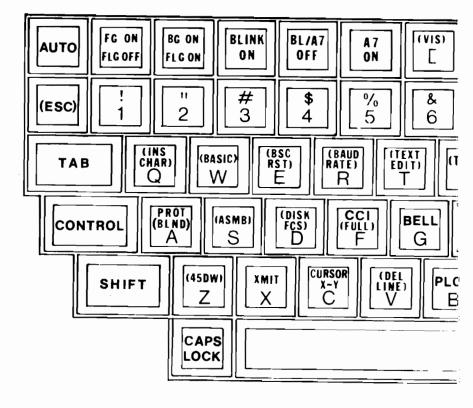

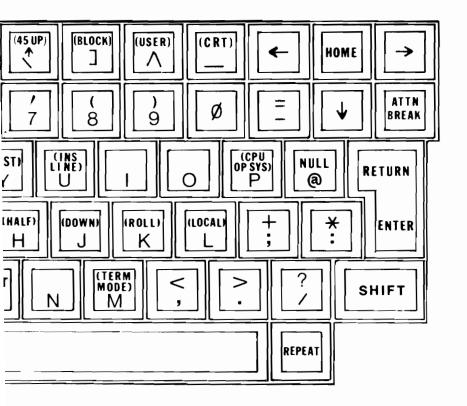

Standard ASCII 4 level, coded with 192 codes. 72 gold crossbar commercial key switches. CPU Reset and Automatic disk loading included.

Optional 101-key and 117-key units include color, numeric and function keys.

## Microcomputer

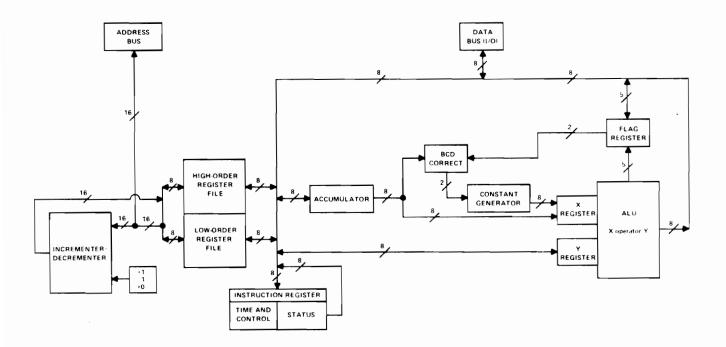

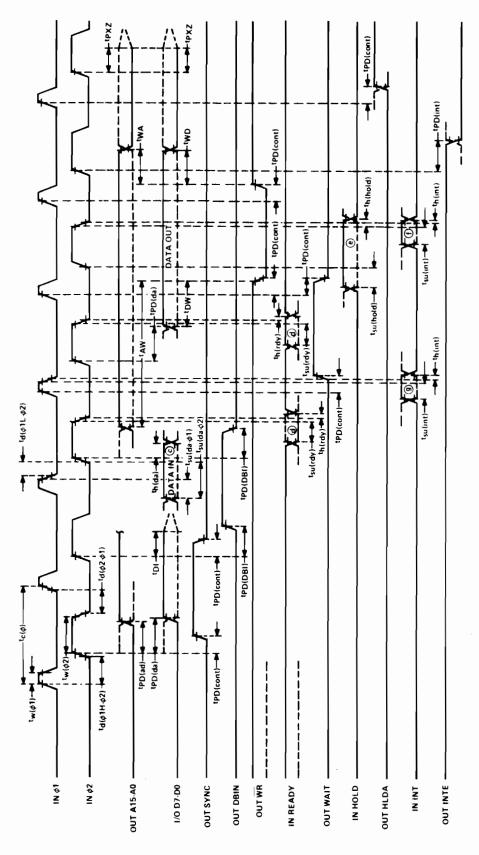

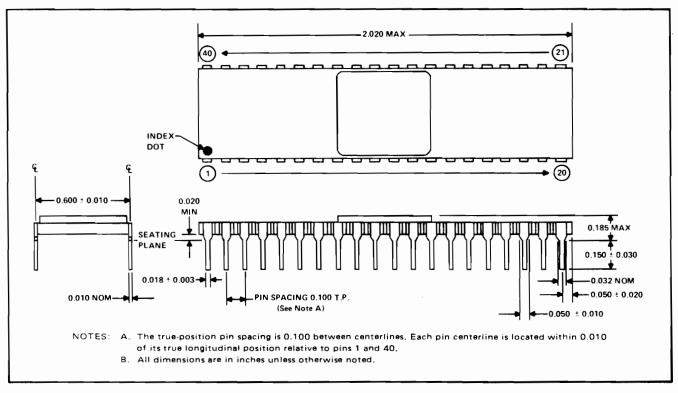

Central Processing Unit, 8080, 2 microsecond CPU with total memory expandable to 64K bytes

Read Only Memory (ROM): 16K bytes of non-destructive read only. Memory sockets included for 12K bytes of additional EPROM/MROM memory. Includes DISK BASIC 8001, File Control System, and Terminal Software.

Random Access Memory (RAM): 4K bytes for screen refresh. 4K bytes for user workspace. Room for 28K bytes of additional user workspace.

Input/Output Ports: System is designed for 512 ports, with 25 ports implemented in standard unit. Optional: one RS-232C Serial Asynchronous Channel for a printer or modem.

Editing: Page/Roll Mode, Erase line, Erase Page, Tab, Caps Lock, CPU Reset, and Color Selection.

Language: DISK BASIC 8001 interpreter in

ROM memory includes: 27 statement types: CLEAR, DATA, DEF, DIM, END, FILE, FOR, GET, GOSUB, GOTO, IF, INPUT, NEXT, ON, OUT, PLOT, POKE, PRINT, PUT, READ, REM, RETURN, RESTORE, STEP, THEN, TO and WAIT. 5 command types: CONT, LIST, LOAD, RUN and SAVE. 18 mathematical functions: ABS(x), ATN(x), CALL(x), COS(x), EXP(x), FRE(x), INT(x), INP(x), LOG(x), PEEK(x), POS(x), RND(x), SGN(x), SIN(x), SPC(x), SQR(x), TAB(x) and TAN(x). 9 string functions: ASC(x\$), CHR\$(x), FRE(x\$), LEFT\$(x\$,I), LEN(x\$), MID\$(x\$,I,J), RIGHT\$(x\$,I), STR(x) and VAL(x). Disk File commands: COPY, DEVICE, DIRECTORY, INITIALIZE, LOAD, PRINT, READ, RENAME, RUN, SAVE and WRITE. Baud Rate: Independent Baud Rate generators for one of 7 Baud rates from 110 Baud to 9.6K Baud.

Disk Drive

Uses 5.25" diskette.

Tracks: 40

Track Density: 48tpi

Access Time: average (40 tracks): 400ms

Average Latency: 200ms

Transfer Rate: 76.8 Kilobits/sec. Performance specifications: Capacity formatted 51.2K Bytes/Side. Both sides

usable by flipping diskette over.

SECTION II

COMPUCOLOR II INSTALLATION

### II. INSTALLATION

Compucolor II is intended for use on a desk or table or any similar vibration free horizontal surface that is free from lint and dust. (However, it is best to avoid metal top desks and the vicinity of large metal objects. Their presence may interfere with proper disk drive performance). It may be used under normal room lighting conditions, although slightly subdued lighting will improve the display appearance (as for a color television set). The Keyboard is usually placed in front of the CRT screen, with the flat, flexible cable running beneath the console to Jl of the Logic Board, accessible through the rear cover. (Note that terminal 2 of the plug goes up). A space 19 inches wide by 24 inches deep is adequate. If the optional additional Disk Drive is used, it may be placed alongside the console (increasing space width by 6 inches) or in some other location within reach of the connecting cable. While no special cooling provisions need be made for Compucolor II, there must be free flow of air around the console—do not place anything on the cabinet that will restrict air flow.

Compucolor II may be used adjacent to most types of electrical equipment and appliances provided it is not within a strong magnetic field. (Operation within a strong magnetic field may disturb operation of the display and transfer of data to or from the diskette).

Unless used with a modem connection to a telephone line, the only external connection is the 6-foot 3 wire power cord to 115VAC power. If connection is to be made to an RS-232 compatible modem, the user provides the necessary cabling. The cable between the Compucolor II and the modem should not exceed 50 feet in length. The terminals on connector J2 at the rear edge of the Logic Board are shown in the table below. The usual modem connections are indicated; however, the modem manufacturer's instructions should be consulted.

| LOGIC BOARD  | MODEM     |                          |

|--------------|-----------|--------------------------|

| J2 TERM. NO. | TERM. NO. | SIGNAL                   |

|              |           |                          |

| 1            | 1         | AA - Protective Ground   |

| 3            | 2         | BA - Transmitted Data    |

| 5            | 3         | BB - Received Data       |

| 7            | 4         | CA - Request to Send     |

| 14           | 7         | AB - Signal Ground       |

| 15           | 20        | CD - Data Terminal Ready |

For a quick check procedure, see "Operational Test" in the MAINTENANCE section (following "ALIGNMENT").

To connect the external Add-on Disk Drive (optional), first disconnect the keyboard cable from the Logic Board. Then connect the add-on drive's cable to the Logic Board's Jl (terminal 2 of the plug up). Now connect the Keyboard cable to the additional connector on the Disk Drive cable (near the Logic Board end).

For information regarding add-on RAM or ROM, see Section  ${\tt V}$ , SUBASSEMBLY DESCRIPTIONS (near end of section).

SECTION III

COMPUCOLOR II OPERATION

# **Compucolor** II Instruction Manual

The Compucolor Corporation thanks you for purchasing a Compucolor II. Although many precautions have been taken to assure that this material is received in good condition, we ask that you take a few minutes to read the following material so that you may derive maximum enjoyment and use from your Compucolor II.

The handbook has been divided into six sections. Section One gives directions for operating the Compucolor II and describes a step by step procedure for loading a program into the Compucolor II from a diskette. Section

Two describes the keyboard and tells you how to write and expand a simple program. Section Three summarizes BASIC and various FCS and CRT commands. Section Four concerns handling and care of diskettes as well as other precautions. Section Five lists a variety of books on the market that deal with computers and programming. Section Six provides lists of port assignments, memory locations, the fifty pin bus and RS232C Interface, as well as a complete character set.

# **Contents**

| SECTION I                                    | Page # |

|----------------------------------------------|--------|

| How to Operate the Compucolor II  SECTION II |        |

| Computer Basics.                             |        |

| Keyboard Operation                           |        |

| What is a program?                           |        |

| Programs can be expanded                     |        |

| SECTION III                                  |        |

| Summary of Commands                          |        |

| 1. CRT COMMANDS                              |        |

| Control Codes.                               | 8      |

| Escape Codes.                                | _      |

| Incremental Direction Codes.                 |        |

| Graphic Plot Submodes.                       |        |

| 2. DISK BASIC                                |        |

| BASIC Statements.                            | 10     |

| BASIC Operators.                             |        |

| Standard Mathematical Functions.             |        |

| Standard String Functions.                   |        |

| BASIC and FILE Error Codes.                  |        |

| 3. FCS (File Control System) COMMANDS.       |        |

| Statement Definitions.                       |        |

| Commands                                     |        |

| FCS Error Codes.                             |        |

| Description of Solution to FCS Errors.       |        |

|                                              |        |

| SECTION IV                                   |        |

| Software                                     |        |

| Precautions                                  |        |

| SECTION V                                    |        |

| Available Literature                         |        |

| SECTION VI                                   |        |

| Port Assignments.                            |        |

| Key Memory Locations.                        |        |

| Fifty Pin Bus                                |        |

| RS232C Interface                             |        |

| Character Set                                |        |

# **Section I**How to operate the Compucolor II

- 1. Place the Compucolor II in a convenient location remembering that you will probably enjoy sitting and playing games on the computer for hours at a time. Be careful not to obstruct the air flow through the vent on the back of the unit.

- 2. Now connect the keyboard cable to the socket labeled "Keyboard" on the back of the Compucolor II. This connector will only fit one way, so if it doesn't fit, turn it over and try pushing in without forcing it. Find the CAPS LOCK key to the left of the space bar on the keyboard. Make sure this key is in the down position (see page 4).

- 3. Next plug the power cord into the back of the computer much like you would plug in an electric frying pan. Then plug the other end of the power cord into the wall-socket. You may need an adapter if your socket cannot take a three-prong insert.

- 4. It's now time to turn on the Compucolor II by pushing to one side the "Power" (white) button on the back of the unit, just above the cord.

- 5. The Compucolor II will require 60 seconds for the tube to warm up before the message "DISK BASIC 8001 V6.78 COPYRIGHT© BY COMPUCOLOR" will appear.

- 6. If it does not appear then hold the SHIFT and CONTROL keys down and press the CPU RESET key. (Note: leave the SHIFT and CONTROL keys down for at least 5 seconds after pressing CPU RESET key.)

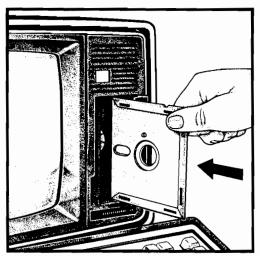

- Take the diskette that came with your Compucolor II and slip it into the right side of the computer. Make sure the diskette is inserted correctly and then close the door. See illustration.

- 8. Push AUTO (brown key in upper left hand corner).

- You will see a list or "MENU" of programs on the screen. Select the program by the number at left. Type in the number and press the ENTER key.

- 10. The program you selected will be loaded into the Compucolor II and you will see directions on the screen on how to proceed with the program you selected. Have fun.

- 11. If nothing appears on the screen after pressing AUTO key try turning the diskette over and follow the instructions starting at step 6.

- 12. If it still doesn't work after trying it again, then simply press the CPU RESET key with no other keys held down. The display will now say, "COMPUCOLOR II CRT MODE V6.78." If this does not appear turn the unit off for 15 seconds and then try from step 4.

- 13. After the "COMPUCOLOR II CRT MODE" message appears, press the (ESC) key and the (BASIC) or letter W key. The following message should appear: "DISK BASIC 8001 V6.78 COPYRIGHT © BY COMPUCOLOR." "MAXIMUM RAM AVAILABLE?"

Now type "8192" and press the ENTER key. (If your Compucolor II is a Model 4 type "16384," then ENTER. If a Model 5, type "32768" then ENTER.) The unit will come back with the amount of free RAM memory available and the "READY" message. Now go to step 7. NOTE: if the ENTER key is pressed without entering a number the unit will search for the maximum RAM in your Compucolor II.

14. If the above does not provide the required results contact your local dealer for assistance, or call Compucolor Corporation's toll-free HOT LINE: (800) 241-4310.

# **Section II**Computer Basics

Compucolor II is a microcomputer. Housed within your Compucolor II is a single integrated circuit chip called a microprocessor. This is the very heart of your Compucolor II. The microprocessor is the computing device for storing programs and for performing logical operations. The microprocessor, called the Central Processing Unit, or CPU, controls all operations of the Compucolor II.

Compucolor II is capable of storing and filing information. Data is fed into the computer by means of typing on the keyboard. This process called INPUT uses the keyboard as its device. To view what has been fed into the computer, Compucolor II uses a display screen called a cathode-ray-tube or CRT display unit to show OLITPLIT.

tube or CRT display unit, to show OUTPUT.

As soon as your Compucolor II is turned on, you are ready to play games, program, store and retrieve informa-

tion. You are in "DISK BASIC 8001." If you followed the instructions on page 2 of this manual you were able to load a diskette and run a program. Now we'd like to re-introduce you to your Compucolor II so that you can communicate with it effectively.

Compucolor II has within it a well defined set of rules for communicating with you. Your task is to learn what the computer already knows. Together, you and Compucolor II will communicate in such a way that Compucolor II will do as you say.

Communicating with Compucolor II means that you will be feeding data or information into your unit by means of a KEYBOARD. Let's take a few minutes to talk about some of the keyboard's features.

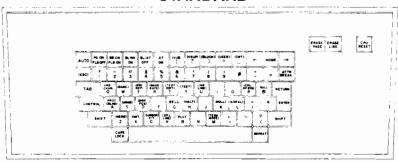

## **STANDARD**

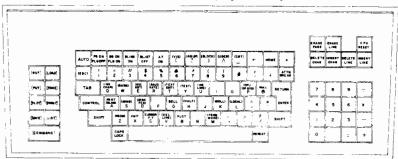

## **EXTENDED** (Optional)

## **DELUXE** (Optional)

# **Keyboard Operation**

## CAPS LOCK

Typing words on the Compucolor II is only done in capital letters. To facilitate the use of capitals, a CAPS LOCK key is used. Located on the left next to the space bar, the CAPS LOCK key will stay depressed and all letters typed will be capitals. By using the SHIFT key. special characters can be printed while the CAPS LOCK key remains depressed. To unlock the CAPS LOCK key, depress it once. The key is now flush with the space bar and special characters are now typed when the SHIFT key is not depressed. With the SHIFT key depressed capital letters are typed. The numbers and punctuation keys work the same as a regular typewriter. SHIFT gives the top character on a key and unshift gives the bottom character on a key.

## SHIFT KEY

Compucolor II's keyboard is much like an ordinary keyboard with some additions. Like a regular typewriter, the SHIFT key is used to type upper case characters and in some cases, special characters. The SHIFT key must be depressed until the desired character is typed.

## **AUTO**

The AUTO key on the upper left has been specially programmed so that when you press the AUTO key a program called "MENU. BAS" will be loaded from the diskette and caused to run. It will list on the screen all programs that can be run under the "MENU" system.

## RETURN ENTER

The RETURN-ENTER key is on the right side of the keyboard. By pressing this key when you are in DISK BASIC you command the Compucolor II to accept the most recent instruction entered. If you are in the "CRT MODE" then this will only cause a carriage return as on a typewriter.

## DIRECTION ARROWS, HOME

Three direction arrows and a HOME key are located on the right side of the keyboard. The HOME key and the arrow keys control the cursor. Pressing HOME brings the cursor to the upper left hand of the screen. The direction arrows are used for correcting typing mistakes or to carry you to another spot on the screen.

To correct a typing error in DISK BASIC press the ← arrow until you have erased the error. This backspace key erases all letters, one at a time, that it touches. For example, if you had typed "NOW IS THE TYME" ← ← retype

"IME"

The following keys must be depressed while the desired key is being pressed:

CONTROL SHIFT REPEAT [COMMAND]

The following key need only be pressed and then followed by pressing the desired

(ESC)

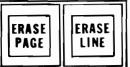

## **ERASE PAGE**

To clear the screen press the ERASE PAGE key. This will return the cursor to its home position and you are ready to start again in the CRT mode. NOTE: in DISK BASIC mode it has erased the screen, but it did not erase your BASIC command internally.

## REPEAT

The REPEAT key next to the space bar allows you to type one letter again and again by typing a letter and holding the REPEAT key down at the same time.

**CPU RESET**The CPU RESET key, on the far right of the keyboard, when pressed, takes you out of the DISK BASIC mode and puts you into the CRT mode. The ESCAPE key

(ESC), located directly below the AUTO key (top left) permits you to go into various special modes by pressing (ESC) and the desired code key. The keys with a name enclosed within ( are standard escape codes. A detailed listing of these codes can be found in Section III.

## ATTN/BREAK (Attention/Break) **KEY**

To temporarily suspend operation when running or listing a BASIC program, press the BREAK key.

To continue, press RETURN or any other character except ↓.

The ↓ or line feed will cause BASIC to break and halt operation.

Use ↓ followed by RETURN to break out of an INPUT statement in BASIC.

NOTE: There is a difference between the number Ø and the letter O, and between the number 1 and the letter L on all computer keyboards.

## What is a Program?

A series of instructions, stored by the computer is called a program.

Programs are written in a simple language called BASIC. The computer already knows this language and with the help of this pamphlet, you will learn some of the BASIC language in order to communicate with Compucolor II.

You're about to write a simple program.

First: Press CPU RESET key while holding down the SHIFT key and the CONTROL key.

Screen display will look like this:

DISK BASIC 8001 V6.78 COPYRIGHT © BY COMPUCOLOR MAXIMUM RAM AVAILABLE? 7473 (or 15665, or 32049) READY

## Now type:

10 PRINT "HI! THIS IS THE START OF SOMETHING WONDERFUL!"

Recheck your typed statement.

- 1. If wrong, use ← key (backspace) to retype.

- 2. If correct, press ENTER key.

- 3. Type RUN and then press the ENTER key.

- 4. If you get an ERROR message, retype the whole line, beginning with 10.

- 5. Press the ENTER key.

- 6. Type RUN and then press the ENTER key.

Did Compucolor follow your instructions?

Congratulations! You have just written your first program!

True, it's only a one-liner, but it is the start of something wonderful!

## **HIGHLIGHTS**

In writing a program every line must have a number. The program is listed on the screen in numerical order, from the smallest to the largest number.

Always use the numeral 8 to type your program numbers. The letter O cannot be substituted for a number. Type PRINT: The computer will print everything that is included within the quotation marks. Press ENTER: This is a command that tells Compucolor II to remember the most recent instruction entered. Type RUN: Any time you want Compucolor II to follow your instructions, you must type RUN and then press

the ENTER key. This causes the Compucolor II to execute the RUN command.

## Programs can be expanded.

In the last section you wrote a one-line program. By adding a second or third line, your program can be expanded.

20 PRINT "CAN YOU BELIEVE THAT I CAN WRITE A PROGRAM?"

Check your work for errors.

Press ENTER

Type RUN and then press the ENTER key.

If all systems worked, the screen display should read:

THIS IS THE START OF SOMETHING WONDERFUL! CAN YOU BELIEVE THAT I CAN WRITE A PROGRAM?

Let us assume that you want to answer the above question-

Type YES

Hit ENTER

Screen display now reads:

SN ERROR.

SN ERROR is the computer's way of telling you that it is not programmed to understand your message. Unless the computer gives you a choice between YES and NO, you cannot enter YES. Sometimes SN ERROR appears even if you do not

intentionally enter misinformation.

Type LIST, press ENTER. Behold! The computer has followed your command and has listed everything that you have

written.

## IF YOUR LISTING HAS A MISTAKE

When you find a mistake, type the number of the line that has the mistake in it. Then retype it correctly and press ENTER. The computer will now incorporate this new line into the program and the original line will be taken out automatically.

The computer's way of telling you that it cannot understand your message.

This allows you to see what you have written up to this point.

## REMEMBER

Do not press SHIFT key. Letters are printed in capitals. Hold SHIFT key down to get special symbols.

Usually the line numbers in a program are written 10 numbers apart. This numbering system permits you to add new information to your program. Sometimes it is easier to read a program output when there is a space between the lines. To put a space between your program lines-

Type 15 PRINT

Press ENTER

Type RUN

When you type PRINT and write nothing after it, the computer will do just that—it will print a blank line. Pretty neat! By adding additional numbers and statements, you can expand your program further. Just type in the number and the computer will automatically put it in the correct numerical sequence.

Now that you have taken part in the excitement of programming, you might want to find out more about it. Section 5 of

this handbook lists some books on programming and games that might interest you.

## HIGHLIGHTS

- 1) Order

- 2) RUN

- SN ERROR

- 4) LIST

- 5) SHIFT key

# **Section III** Summary of Commands

## 1. CRT COMMANDS

**CONTROL CODES**

| CODE                                 | EXPLANATION                                                                                                                                                                                                                                   |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-NULL (control @)                   | Has no effect.                                                                                                                                                                                                                                |

| 1-AUTO (control A)                   | Loads and runs a BASIC program named "MENU," from the disk drive.                                                                                                                                                                             |

| 2-PLOT (control B)                   | Enters graphic plot mode (see plot submodes), not allowed as a BASIC input character.                                                                                                                                                         |

| 3-CURSOR XY (control C)              | Enters X-Y cursor address mode for either visible cursor or blind cursor, used to go from BASIC to CRT MODE when typed as a BASIC input character.                                                                                            |

| 4-(control D)                        | Not used.                                                                                                                                                                                                                                     |

| 5-(control E)                        | Not used.                                                                                                                                                                                                                                     |

| 6-CCI (control F)                    | The next character which follows provides the 8 bit visible status word. Specifies Foreground, Background, Blink, and Plot. (See status word format, page 9.)                                                                                 |

| 7—BELL (control G)                   | Not used.                                                                                                                                                                                                                                     |

| 8-HOME (control H)                   | Moves the cursor to top left corner of display.                                                                                                                                                                                               |

| 9-TAB (control I)                    | Causes cursor to advance to next column—the tab columns are every 8 characters.                                                                                                                                                               |

| 10-↓ (control J) or<br>LINEFEED      | Causes a break in BASIC execution of a program, causes the cursor to move down one line.                                                                                                                                                      |

| 11—ERASE LINE (control K)            | Causes the cursor to return to beginning of line and causes the complete line to be erased. Also causes the BASIC input line to be ignored.                                                                                                   |

| 12-ERASE PAGE (control L)            | Causes the complete screen to be erased and the cursor moves to the home position. BASIC input ignores this character.                                                                                                                        |

| 13—RETURN (control M)                | Causes the cursor to move to the beginning of the line it presently is on. Causes BASIC input to accept the typed line and process as a statement or input data.                                                                              |

| 14-A7 ON (control N)                 | Turns the A7 flag on. (2x character height and also 1 stop bit.)                                                                                                                                                                              |

| 15-BLINK/A7 OFF (control O)          | Turns the blink bit and A7 flag off.                                                                                                                                                                                                          |

| 16-BLACK KEY (control P)             | Sets foreground color black if flag is off and background black if flag is on.                                                                                                                                                                |

| 17—RED KEY (control Q)               | Same as above with color red.                                                                                                                                                                                                                 |

| 18—GREEN KEY (control R)             | Same as above with color green.                                                                                                                                                                                                               |

| 19-YELLOW KEY (control S)            | Same as above with color yellow.                                                                                                                                                                                                              |

| 20-BLUE KEY (control T)              | Same as above with color blue.                                                                                                                                                                                                                |

| 21-MAGENTA KEY (control U)           | Same as above with color magenta.                                                                                                                                                                                                             |

| 22-CYAN KEY (control V)              | Same as above with color cyan.                                                                                                                                                                                                                |

| 23—WHITE KEY (control W)             | Same as above with color white.                                                                                                                                                                                                               |

| 24—XMIT (control X)                  | Causes data to be transmitted from the visible cursor to the end of the page or until FF, ØØ sequence is found in refresh RAM. Sends text characters with a linefeed and carriage return at end of each line. NOTE: color status is not sent. |

| 25-CURSOR RIGHT (control Y)          | Causes the cursor to move right 1 position. On BASIC input displays previous character inputted.                                                                                                                                              |

| 26-CURSOR LEFT (control Z)           | Causes the cursor to move left 1 position. On BASIC input deletes previous character from input buffer.                                                                                                                                       |

| 27-ESC (control [)                   | Provides an entry to the escape code table—must be followed by one or more codes for proper operation.                                                                                                                                        |

| 28-CURSOR UP (control \)             | Causes the cursor to move up one line.                                                                                                                                                                                                        |

| 29-FG ON/FLAG OFF (control ])        | Sets the flag bit off. If followed by one of the color keys it will set the foreground to that color. In plot mode OR's "ON" bits.                                                                                                            |

| 30-BG ON/FLAG ON (control $\wedge$ ) | Sets the flag bit on. If followed by one of the color keys, it will set the background to that color. In plot mode XOR's "ON" bits.                                                                                                           |

| 31-BLINK ON (control -)              | Sets the blink bit on which will blink the foreground color against the background color.                                                                                                                                                     |

## **ESCAPE CODES**

| 5 BIT CODE | LETTER | FUNCTION                                                                                   |

|------------|--------|--------------------------------------------------------------------------------------------|

| 0          | @      | Used for terminal control—not available for any other use.                                 |

| 1          | A      | Blind cursor mode.                                                                         |

| 2          | В      | Plot via color pad.                                                                        |

| 3          | С      | Transmit cursor X, Y position to RS232 PORT.                                               |

| 4          | D      | Enters Disk File Control System (FCS) with CRT as output.                                  |

| 5          | E      | Re-entry to DISK BASIC.                                                                    |

| 6          | F      | Sets full duplex mode, not functional when in BASIC.                                       |

| 7          | G      | Enters Disk File Control System (FCS) with RS232 PORT as output.                           |

| 8          | н      | Sets half duplex mode.                                                                     |

| 9          | 1      | Causes a program jump to location 36864.                                                   |

| 10         | J      | Sets write vertical mode.                                                                  |

| 11         | K      | Sets roll up and write left to right mode.                                                 |

| 12         | L      | Sets local mode.                                                                           |

| 13         | М      | Sets all output to the RS232 PORT.                                                         |

| 14         | N      | Sets to ignore all inputs.                                                                 |

| 15         | 0      | Not used.                                                                                  |

| 16         | P      | Not used.                                                                                  |

| 17         | Q      | Not used.                                                                                  |

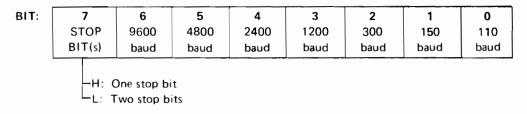

| 18         | R      | Baud rate selection mode. A7 on = 1 stop bit, A7 off = 2 stop bits. (See baud rate table.) |

| 19         | S      | Causes a program jump to location 40960.                                                   |

| 20         | T      | Causes a program jump to location 33280.                                                   |

| 21         | U      | Not used.                                                                                  |

| 22         | V      | Not used.                                                                                  |

| 23         | w      | Initializes and transfers control to DISK BASIC 8001.                                      |

| 24         | X      | Sets terminal to page mode and write left to right mode.                                   |

| 25         | Y      | Test mode—fill page with next character.                                                   |

| 26         | Z      | Not used.                                                                                  |

| 27         | [      | Visible cursor mode.                                                                       |

| 28         | 1      | Not used.                                                                                  |

| 29         | ]      | Not used.                                                                                  |

| 30         | ٨      | Causes a program jump to location 33275.                                                   |

| 31         | _      | Transfer control to the CRT mode.                                                          |

## **BAUD RATE SELECTION**

| Number    | 1   | 2   | 3   | 4    | 5    | 6    | 7    |

|-----------|-----|-----|-----|------|------|------|------|

| Baud rate | 110 | 150 | 300 | 1200 | 2400 | 4800 | 9600 |

## STATUS WORD FORMAT

| <b>A</b> <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao  |

|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|

| Plot                  | Blink          | В              | ackground Col  | or             | F              | oreground Col  | or  |

|                       |                | Blue           | Green          | Red            | Blue           | Green          | Red |

## INCREMENTAL DIRECTION CODES

| If BIT = 1  |

|-------------|

| Direction   |

| Value (Hex) |

| $\Delta$       | <u>.X1</u>     | $\Delta$       | <u>.Y1</u>     | Δ              | X2             | Δ'             | <b>Y</b> 2 |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|

| A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Αo         |

| +              | 1              | +              |                | +              | _              | +              | _          |

| 80             | 40             | 20             | 10             | 8              | 4              | 2              | 1          |

## **GRAPHIC PLOT SUBMODES**

| DISK BASIC plot value<br>or<br>RS-232 INPUT CODE | PLOT<br>SUBMODE            | OPTIONAL<br>FUNCTION<br>KEYBOARD CODE |

|--------------------------------------------------|----------------------------|---------------------------------------|

| 255                                              | Plot Mode Escape           | F 15                                  |

| 254                                              | Character Plot             | F 14                                  |

| ,253 <sub>\</sub>                                | X Point Plot               | F 13                                  |

| (252)                                            | Y Point Plot               | F 12                                  |

| 251                                              | X-Y Incremental Point Plot | F 11                                  |

| 250,                                             | X₀ of X Bar Graph          | F 10                                  |

| ,249                                             | Y of X Bar Graph           | F 9                                   |

| (248)                                            | X max of X Bar Graph       | F 8                                   |

| 247                                              | Incremental X Bar Graph    | F 7                                   |

| 246 <sub>\</sub>                                 | Y₀ of Y Bar Graph          | F6                                    |

| ,245                                             | X of Y Bar Graph           | F 5                                   |

| 244                                              | Y max of Y Bar Graph       | F 4                                   |

| 243                                              | Incremental Y Bar Graph    | F3                                    |

| ,242 <sub>\</sub>                                | X <sub>0</sub> Vector Plot | F 2                                   |

| 241                                              | Y₀ Vector Plot             | F 1                                   |

| 240                                              | Incremental Vector Plot    | FØ                                    |

For incremental plot submodes see the format of the incremental direction codes (page 9).

## 2. DISK BASIC

BASIC Statements

The following summary of BASIC statements defines the general format for the statement and gives a brief explanation of its use.

| COMMAND                                                                              | EXPLANATION                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLEAR                                                                                | Sets the array and string buffers to nulls and zeroes.                                                                                                                                                 |

| CLEAR X                                                                              | Sets space for string variable to X characters (normally 50 characters).                                                                                                                               |

| CONT                                                                                 | Continues execution after CTRL/J, or $\psi$ .                                                                                                                                                          |

| DATA value list                                                                      | Used in conjunction with READ to input data into an executing program.                                                                                                                                 |

| DEF FN X (argument) = expression                                                     | Defines a user function to be used in the program.                                                                                                                                                     |

| DIM variable (n), variable (n,m),<br>variable \$(n), variable \$(n,m)                | Reserves space for lists and tables according to subscripts specified after variable name. Up to 255 dimensions.                                                                                       |

| END                                                                                  | Terminates program execution.                                                                                                                                                                          |

| FILE "N", "filename", records, rec. size, blocking factor                            | Creates a new random file with the specified number of records (1-32767), record size (1-32767 bytes), and blocking factor (1-255). File name is a string expression containing a valid FCS file name. |

| FILE "R", file number, "filename", buffers                                           | Opens a random file with the specified file number (1-127) and number of buffers (1-255).                                                                                                              |

| FILE "A", file, current rec., records, rec. size, blocking factor                    | Finds the specified attributes for the currently open file: current record accessed, number of records, record size, and blocking factor.                                                              |

| FILE "C", file 1,, file N                                                            | Closes the specified files and releases the buffer space.                                                                                                                                              |

| FILE "D", file 1,, file N                                                            | Writes any modified buffers immediately for the specified files.                                                                                                                                       |

| FILE "T", line number                                                                | Causes file errors to trap to the specified line number. No line number turns the error trapping off.                                                                                                  |

| FILE "E", file, error, line number                                                   | Lets the user determine the disk error number and location of the file error.                                                                                                                          |

| FOR variable = expression 1 TO expression 2 STEP expression 3                        | Sets up a loop to be executed the specified number of times.                                                                                                                                           |

| GET file N, record, first byte;<br>numeric variable, string variable<br>[byte count] | Reads from the record in the file N starting at the specified first byte (1-255) into the variables in the list. String variables must have a byte count (1-255).                                      |

| BASIC | Statement | ts (Cont.) |

|-------|-----------|------------|

|-------|-----------|------------|

| BASIC Statements (Cont.)                                                       |                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMMAND                                                                        | EXPLANATION                                                                                                                                                                                                       |

| GOSUB line number                                                              | Used to transfer control to the first line of a subroutine.                                                                                                                                                       |

| GOTO line number                                                               | Used to unconditionally transfer control to other than the next sequential line in the program.                                                                                                                   |

| IF expression GOTO line number                                                 | Used to conditionally transfer control to the specified line of the program.                                                                                                                                      |

| IF expression THEN statement                                                   | Used to execute BASIC statements only when expression is true.                                                                                                                                                    |

| INPUT list                                                                     | Used to input data from the terminal keyboard, prompts with "?".                                                                                                                                                  |

| INPUT "string"; list                                                           | Used to input data with the quoted string as the prompt.                                                                                                                                                          |

| LIST                                                                           | Prints the user program currently in memory on the CRT display.                                                                                                                                                   |

| LIST line number                                                               | Prints the program from the line specified to the end.                                                                                                                                                            |

| LOAD "PRGRM1"                                                                  | Loads a BASIC Program named "PRGRM1" from disk into memory. Names cannot exceed six characters (letters and/or numbers).                                                                                          |

| LOAD "name.ARY"                                                                | Loads the numeric array specified by name from disk. First two characters are the array's name.                                                                                                                   |

| NEXT variable                                                                  | Placed at the end of a FOR loop to return control to the FOR statement.                                                                                                                                           |

| ON X GOSUB line number list                                                    | Multiple GOSUB statement. Will transfer control to subroutine on stated line. However, the RETURN statement placed at the end of each subroutine will cause the next statement following ON GOSUB to be executed. |

| ON X GOTO line number list                                                     | Multiple GOTO statement, will transfer control to stated line number, depending on value of variable.                                                                                                             |

| OUT I,X                                                                        | Causes the byte X to be output to port I (the range of I is 0 to 255).                                                                                                                                            |

| PLOT expression                                                                | Sends the one byte result of the expression to the terminal. The result must be between 0 and 255.                                                                                                                |

| PLOT list                                                                      | Sends the list of data to the CRT. Example: PLOT 2, 242, 0, 0, 255.                                                                                                                                               |

| POKE I,X                                                                       | Causes the byte X to be placed in memory location I, the range of I is 0 to 65535.                                                                                                                                |

| PRINT list                                                                     | Used to output data to the terminal.                                                                                                                                                                              |

| PRINT expression                                                               | Prints results of expression.                                                                                                                                                                                     |

| PRINT expression, expression;                                                  | The ; causes the carriage return and line feed to be suppressed. Use , for normal spacing and ; for compressed spacing.                                                                                           |

| PRINT "string"                                                                 | Prints a character string.                                                                                                                                                                                        |

| ?                                                                              | Equivalent to the word PRINT.                                                                                                                                                                                     |

| PRINT SPC (X)                                                                  | Prints the specified number of spaces.                                                                                                                                                                            |

| PRINT TAB (X)                                                                  | Used to space to the specified column.                                                                                                                                                                            |

| PUT file N, record, first byte;<br>numeric expr., string expr.<br>[byte count] | Writes the expressions in the list to the record in file N starting at the specified first byte. String expressions must have a byte count.                                                                       |

| READ variable list                                                             | Used to assign the values listed in a DATA statement to the specified variables.                                                                                                                                  |

| REM comment                                                                    | Used to insert explanatory comments into a BASIC program.                                                                                                                                                         |

| RESTORE                                                                        | Used to reset the data block pointer so the same data can be used again.                                                                                                                                          |

| RESTORE line number                                                            | Used to reset the data block pointer to a specified line number.                                                                                                                                                  |

| RETURN                                                                         | Used to return program control to the statement following last executed GOSUB statement.                                                                                                                          |

| RUN                                                                            | Executes the program in memory.                                                                                                                                                                                   |

| RUN line number                                                                | Executes the program starting at line number specified.                                                                                                                                                           |

| SAVE "PRGRM1"                                                                  | Saves the BASIC program or data from memory into the disk and names it "PRGRM1."                                                                                                                                  |

| SAVE "name. ARY"                                                               | Saves the numeric array specified by name on disk. First two characters are the array's name.                                                                                                                     |

| WAIT X,I,J                                                                     | Causes the input port X to be read, exclusive OR'ed with byte J, and then AND'ed with byte I. The program will wait until the result is zero before continuing.                                                   |

| :                                                                              | A colon is used to separate multiple statements per line.<br>Example 10 A = 1: B = $10$ : C = $111$                                                                                                               |

## **BASIC Operators**

| SYMBOL                                   | FUNCTION                                                                        |

|------------------------------------------|---------------------------------------------------------------------------------|

| =                                        | Assignment, or equality test (DISK BASIC 8001 does not allow the LET statement) |

| _                                        | Negation or subtraction                                                         |

| +                                        | Addition or string concatenation                                                |

| *                                        | Multiplication                                                                  |

| /                                        | Division                                                                        |

| ٨                                        | Exponentiation                                                                  |

| NOT                                      | Logical or One's complement (2 byte integer)                                    |

| AND                                      | Logical or Bitwise AND (2 byte integer)                                         |

| OR                                       | Logical or Bitwise OR (2 byte integer)                                          |

| =, <, >,<br>< =, = <,<br>> =, = >,<br><> | Relational tests (result is TRUE = $-1$ or FALSE = $0$ )                        |

| (1) Expressio  | ns in parentheses                  |

|----------------|------------------------------------|

| (2) Exponenti  | iation (A ^ B)                     |

| (3) Negation   | (-X)                               |

| (4)*,/         |                                    |

| (5) +,-        |                                    |

| (6) Relational | operators (=, < >, <, >, < =, > =) |

| (7) NOT        |                                    |

| (8) AND        |                                    |

| (9) OR         |                                    |

$\begin{tabular}{ll} \textbf{Standard Mathematical Functions} \\ \textbf{The Mathematical functions are of the following form: 10y = ABS (x).} \\ \end{tabular}$

| NAME    | EXPLANATION                                                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABS(x)  | Returns the absolute value of X.                                                                                                                               |

| ATN(x)  | Returns the arctangent of x as an angle in radians in the range $+$ or $-$ pi/2. Where pi $=$ 3.14159.                                                         |

| CALL(x) | Call the user machine language routine at location 33282. D,E registers have value of X and A,B registers must have Y on return from machine language routine. |

| COS(x)  | Returns the cosine of x radians.                                                                                                                               |

| EXP(x)  | Returns the value of $e^{x}$ where $e = 2.71828$ .                                                                                                             |

| FNx(y)  | Returns the value of the user defined function x with argument y.                                                                                              |

| FRE(x)  | Returns number of free bytes not in use.                                                                                                                       |

| INT(x)  | Returns the greatest integer less than or equal to x.                                                                                                          |

| INP(x)  | Returns a byte from input port x. The range for x is 0 to 255.                                                                                                 |

| LOG(x)  | Returns the natural logarithm of x.                                                                                                                            |

| PEEK(x) | Returns a byte from memory address x. The range for x is 0 to 65535.                                                                                           |

| POS(x)  | Returns a value 0 to 63 of the print command column.                                                                                                           |

| RND(x)  | Returns a random number between 0 and 1.                                                                                                                       |

| SGN(x)  | Returns a value indicating the sign of x.                                                                                                                      |

| SIN(x)  | Returns the sine of x radians.                                                                                                                                 |

| SQR(x)  | Returns the square root of x.                                                                                                                                  |

| TAN(x)  | Returns the tangent of x radians.                                                                                                                              |

Standard String Functions

The string functions are of the following form A\$ = CHR\$(x) or A = ASC(x\$)

| NAME           | EXPLANATION                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------|

| ASC(x\$)       | Returns as a decimal number the eight-bit internal code for the first character of string (x\$). |

| CHR\$(x)       | Generates a one-character string having the ASCII value of x.                                    |

| FRE(x\$)       | Returns number of free string bytes.                                                             |

| LEFT\$(x\$,I)  | Returns left most I characters of string (x\$).                                                  |

| LEN(x\$)       | Returns the number of characters in the string (x\$).                                            |

| MID\$(x\$,I,J) | Returns J characters of string (x\$) starting at position I.                                     |

| RIGHT\$(x\$,I) | Returns right most I characters of string (x\$).                                                 |

| STR\$(x)       | Returns the string which represents the numeric value of x.                                      |

| VAL(x\$)       | Returns the number represented by the string (x\$).                                              |

## **BASIC and FILE Error Codes**

After an error occurs, BASIC returns to command level and types READY. Variable values and the program text remain intact, but the program cannot be continued and all GOSUB and FOR context is lost.

When an error occurs in a direct statement, no line number is printed.

Format of error messages:

Direct Statement

XX ERROR

Indirect Statement

XX ERROR IN YYYYY

In both of the above examples, "XX" will be the error code. The "YYYYY" will be the line number where the error occured for the indirect statement.

The following are the possible error codes and their meanings:

|            | are ANIALO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERROR CODE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BS         | Bad Subscript. An attempt was made to reference a matrix element which is outside the dimension of the matrix. This error can occur if the wrong number of dimensions are used in a matrix reference. For instance, $A(1,1,1) = Z$ when A has been dimensioned DIM $A(2,2)$ .                                                                                                                                                                                                                                                              |

| DD         | Double Dimension. After a matrix was dimensioned, another dimension statement for the same matrix was encountered. This error often occurs if a matrix has been given the default dimension 10 because a statement like $A(I) = 3$ is encountered and then later in the program a DIM $A(100)$ is found.                                                                                                                                                                                                                                   |

| CF         | Call Function error. The parameter passed to a math or string function was out of range. CF errors can occur due to:  a) A negative matrix subscript (A(−1)=0). b) An unreasonably large matrix subscript (>32767). c) LOG-negative or zero argument. d) SQR-negative argument. e) A↑B with A negative and B not an integer. f) A CALL (X) before the address of the machine language subroutine has been patched in. g) Calls to MID\$, LEFT\$, RIGHT\$, INP, OUT, WAIT, PEEK, POKE, TAB, SPC or ON GOTO/GOSUB with an improper argument. |

| ID         | Illegal Direct. You cannot use an INPUT or DEF statement as a direct command.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NF         | NEXT without FOR. The variable in a NEXT statement corresponds to no previously executed FOR statement.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OD         | Out of Data. A READ statement was executed but all of the DATA statements in the program have already been read. The program tried to read too much data or insufficient data was included in the program.                                                                                                                                                                                                                                                                                                                                 |

| ОМ         | Out of Memory. Program too large, too many variables, too many FOR loops, too many GOSUB's, too complicated an expression or any combination of the above.                                                                                                                                                                                                                                                                                                                                                                                 |

| ov         | Overflow. The result of a calculation was too large to be represented in BASIC's number format. If an underflow occurs, zero is given as the result and execution continues without any error message being printed.                                                                                                                                                                                                                                                                                                                       |

| SN         | Syntax error. Missing parenthesis in an expression, illegal character in a line, incorrect punctuation, etc.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RG         | RETURN without GOSUB. A RETURN statement was encountered without a previous GOSUB statement being executed.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| US         | Undefined Statement. An attempt was made to GOTO, GOSUB or THEN to a statement which does not exist.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

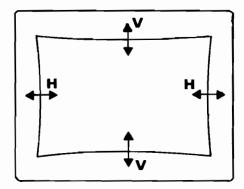

| /0         | Division by Zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |